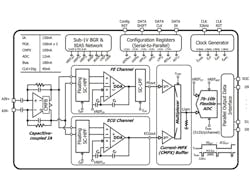

At the International Solid-State Circuits Conference (ISSCC) in January, researchers from IMEC in Belgium, the Catholic University of Leuven, Belgium, the Technology University of Eindhoven in the Netherlands, and Olympus Corporation in Tokyo, described a tiny, ultra-low-power analog signal processor (ASP) for heart-rate monitoring in implantable pacemakers. (See figure above.) Pacemakers need such functionality to sense cardiac rhythm disorders.

Essentially, the ASP executes a DSP function to extract the timings of three points: Q, R, and S, in the electrical signature of each heartbeat. (i/e., the signature of the heart itself, not the timing pulse from the pacemaker.)

To reduce power consumption, the team shifted the functionality of QRS-band power parameter extraction to the analog domain. They also developed a current-multiplexed ADC driver and a flexible ADC. As a result, the power consumption of the ASP is less than 1μW. This had little or no effect on ac performance, with SNR less than 70 dB, CMRR less than 90 dB, and PSRR below 80 dB.

The paper, “680nA Fully Integrated Implantable ECG- Acquisition IC with Analog Feature Extraction” is from ISSCC-2014 Session 24.