Safety critical systems need to be built on silicon that has also been certified to meet safety critical standards. This means the design must follow strict guidelines in addition to incorporating hardware to catch errors that conventional designs would not.

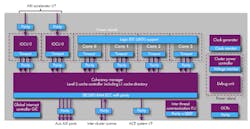

Imagination Technologies’ MIPS I6500-F core (Fig. 1) targets safety critical applications such as self-driving cars, the Industrial Internet of Things (IIoT), and robotics. It is compliant with the ISO 26262 and IEC 61508 standards and designed to meet system-level ASIL D functional safety standards. The multicore architecture incorporates parity, timeout support, and built-in self-test (BIST) throughout.

The I6500 core uses simultaneous multi-threading (SMT) with a 9-stage, superscalar, dual-issue design and four threads per core. Instruction bonding combines sequential integer or floating point loads or stores into a single operation, doubling memory-intensive data move performance.

There is an optional dual-issue FPU/SIMD unit with 32 128-bit registers, with support for 8-/16-/32-/64-bit integer and fixed point plus IEEE-754 2008 compliant 16-/32-/64-bit floating point data. The core supports hardware virtualization (VZ) allowing “zero context switching” for real-time response. Scratchpad memory options allow the architecture to handle deterministic code execution, even with VZ and SMT support. Designs can incorporate up to 1 Mbyte of scratchpad RAM, plus up to 64 Kbytes of 4-way set associative L1 cache with ECC support.

Imagination’s OmniShield security architecture supports isolation of programs and peripherals. The virtualized global interrupt controller (GIC) allows OmniShield to provide interrupts with a controlled group of peripherals and applications.

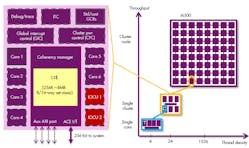

The architecture is designed to work within Imagination’s cluster architecture (Fig. 2) that allows up to eight cores to be combined in a cluster node. Nodes can also incorporate I/O coherency units (IOCU). A cluster can have up to 64 nodes.