Hybrid Emulation Accelerates Architecture Optimization, Software Development, And Software-Driven Verification

Mobile and Internet of Things (IoT) devices and their supporting infrastructure are driving the system-on-chip (SoC) design challenge with demanding specifications, increasing software content, and aggressive development schedules. Design teams can’t afford mistakes when making critical architecture decisions impacting performance or other requirements early in the development processes. Software teams need a high-speed model of the SoC months ahead of silicon availability to begin application development. Verification teams need higher-performance execution platforms to complete verification on time, especially when faced with long-running, multi-billion-cycle software-driven tests.

Related Articles

- Multi-Billion_Cycle Tests Require Comprehensive Debug

- Verification And Software Dominate EDA's Future

- Multicore SoCs Make Emulation Mandatory

Virtual prototypes, incorporating high-performance transaction-level models of an SoC, have emerged over the past few years as a powerful tool for enabling architecture optimization and early software development. Before the new RTL-based (register transfer level) platform is available, key design decisions can be evaluated to ensure performance and other specifications are met. Software developers can use functional models as a target against which to develop and test operating system (OS), driver, and application software long before silicon is available. However, transaction-level models sometimes don’t exist for new, legacy, or third-party blocks in the SoC, hindering architecture optimization and delaying the start of software development.

This file type includes high resolution graphics and schematics when applicable.

Emulation has become an essential tool for verifying complex SoCs with huge software content. Emulators can execute detailed models of a design some 10,000 times faster than hardware description language (HDL) simulators, enabling multi-billion-cycle tests to be run in hours instead of days or weeks. The latest generation of high-performance emulators, such as Synopsys’ ZeBu Server-3, can routinely achieve multi-megahertz performance, enabling even shorter runtimes for software-driven tests. But verification teams sometimes don’t have access to critical intellectual property (IP) RTL sources and seek new approaches for higher emulation performance.

Hybrid emulation is a relatively new technique that combines emulation and virtual prototyping to enable earlier architecture optimization and software development, as well as higher performance for software-driven RTL verification even when critical IP RTL isn’t available (Fig. 1). For the hardware architect, it enables RTL blocks or subsystems running in an emulator to serve as a high-performance, cycle-accurate model for SoC performance analysis and architecture optimization. For the software developer, it can enable a virtual prototype to be brought up even if transaction-level models don’t exist. Blocks with missing models can be run at high speed in the emulator. For the verification engineer, pre-verified processor subsystem blocks can be moved out of the emulator and executed on the host platform using a virtual prototype of the processor subsystem, freeing up capacity on the emulator while increasing overall performance.

Accelerating Architecture Validation

In a hybrid emulation environment, an architecture exploration tool such as Platform Architect MCO is connected to a high-speed emulation system through a SystemC TLM-2.0 interface to the emulator’s transaction-based verification environment. This enables virtual prototyping users to link their SystemC architecture model to RTL models that will give them cycle accuracy and faster runtime performance for architecture validation (Fig. 2).

One common approach uses early architecture exploration and optimization with SystemC transaction-level models representing the application traffic, the SoC interconnect, and the memory subsystems in Platform Architect MCO. Then, to validate the candidate architecture, the traffic-based workloads are replaced with application software tests running on the cycle-accurate processor RTL in the ZeBu Server-3 emulator. The SystemC interconnect and memory subsystem models available inside Platform Architect MCO can continue to be leveraged through the high-performance hybrid connection. In addition to the processors, any design blocks only available as RTL, such as third-party IP or in-house design reuse blocks, can be modeled on the emulator. For architecture validation, it’s important that the hybrid emulation environments allow users to set the timing synchronization mode of the interface between the two environments to the level of accuracy required.

Architectural Validation

For SoC architecture validation, where a user links the high-performance emulator like ZeBu Server-3 to a virtual prototype exploration tool like Platform Architect MCO, testing typically consists of running application software tests on the processor subsystems in the emulator to drive the simulation and monitoring performance to confirm that the optimized configuration of the architecture design chosen during exploration meets the required performance metrics.

The interconnect and memory subsystem peripherals often are modeled in Platform Architect MCO, with cycle-accurate CPU subsystems modeled in ZeBu Server-3. In the ZeBu world, all the various timing domains would maintain their relative clock ratios. Operation in a fully timed synchronization mode provides full cycle accuracy.

Users then can use this environment to run a variety of processing loads and data streams and quickly analyze relative performance tradeoffs between various factors like the cache sizes and number of processors. Typical results might show the impact on performance of variations in the number of data streams and the processing loads.

Early Software Development And Software-Driven Verification

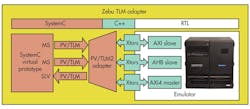

Hybrid emulation is also valuable to enable pre-silicon software development while some of the RTL design is still under development and for system-level hardware-software co-verification (Fig. 3). Virtual prototypes support the use of instruction-accurate, SystemC/C++ processor models and other loosely timed SystemC TLM-2.0 models. Such models remove the need to wait for silicon to begin developing or validating system software.

The software team can leverage these functional models in a virtual prototype developed using Synopsys Virtualizer (the resulting software development kit is called a VDK: Virtualizer Development Kit), with some pieces of the design for which no SystemC models exist represented as RTL in a high-performance emulator like ZeBu Server-3. This hybrid emulation environment allows the software design team to begin developing, running, and testing its software at multi-megahertz speeds long before silicon is available.

This hybrid emulation mode is also valuable for software-driven verification when the RTL for the processors is not available or when one wishes to free up some of the emulation system capacity by offloading the processor emulation models and other blocks of the design to the virtual prototype.

A SystemC loosely timed processor model must describe the processor behavior accurately enough to execute real, unmodified software images and model how the system would boot the operating system, support actual drivers, and run applications. Hybrid emulation with a high-performance emulator can run at multi-megahertz speeds, fast enough to provide a productive debugging experience.

When using the hybrid emulation system for software development, one requires access to the full visibility debug features of the emulator where some of the design is modeled. This allows a full system level view for verification.

In the hybrid emulation environment, while the processor models are executing software in the virtual prototype, the emulator also provides the full visibility into the design’s RTL to allow simultaneous verification of the non-processor design elements. In such environments, typically the embedded software is performing as an executable test bench in combination with emulation focused transaction-level tests using virtual components, C++ testbenches, software traffic/packet generators, or physical testers.

To achieve the hybrid emulation speed required for software development and testing within the virtual prototype, several parameters are not typically modeled with 100% accuracy in a virtual prototype, such as detailed timing. Consequently, the synchronization mode for hybrid emulation for software development is generally loosely timed or approximately timed, which can still provide the accuracy level needed for software development as well as the performance expected.

Software Development Or Software-Driven Verification

In using hybrid emulation for software development or software-driven verification, the processors are modeled in the virtual prototype using SystemC loosely timed models, such as ARM Fast Models, while major pieces of the design may be modeled in the emulator. The processors and subsystems are connected to the emulated RTL blocks through transactors for the bus level communications with a TLM-2.0 wrapper or adapter. Software debug is accomplished using traditional software development tools such ARM DS-5, Lauterbach Trace32, or inherent tools of the virtual prototype environment.

Summary

Hybrid emulation offers numerous benefits for SoC architecture, software, and verification teams.

For architects, hybrid emulation provides a mechanism to implement key elements of the SoC that are only available as RTL in a high-performance, cycle-accurate manner to support their architecture optimization efforts. Users can choose cycle-accurate, approximately timed, or loosely timed synchronization between the virtual prototype and the emulator to make speed/accuracy tradeoffs.

For software development teams, hybrid emulation enables users to perform multi-core software debug in a very high-performance environment without waiting for silicon or all transaction-level models to be available.

For verification teams, hybrid emulation enables high-performance software-driven verification even when processor RTL is not available for emulation, while freeing emulator capacity by moving processor models to the virtual prototype.

Hybrid emulation enables SoC development teams to take full advantage of their investment in a high-performance emulation system across their entire project to better meet increasing software, verification, and competitive challenges.

Tom Borgstrom is a director of marketing at Synopsys, where he is responsible for the ZeBu emulation solution. Before assuming his current role, he was director of strategic program management in Synopsys’ Verification Group. Prior to joining Synopsys, he held a variety of senior sales, marketing, and applications roles at TransEDA, Exemplar Logic, and CrossCheck Technology and worked as an ASIC design engineer at Matsushita. He received bachelor’s and master’s degrees in electrical engineering from the Ohio State University.

About the Author

Tom Borgstrom

Director of Marketing

Tom Borgstrom is a director of marketing at Synopsys, where he is responsible for the ZeBu emulation solution. Before assuming his current role, he was director of strategic program management in Synopsys’ Verification Group. Prior to joining Synopsys, he held a variety of senior sales, marketing, and applications roles at TransEDA, Exemplar Logic, and CrossCheck Technology and worked as an ASIC design engineer at Matsushita. He received bachelor’s and master’s degrees in electrical engineering from the Ohio State University.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: