Interview: Josh Lee Addresses DDR And Self Calibrating Logic

Josh Lee is president and CEO of Uniquify. Uniquify has developed IP for building high performance DDR subsystems. The systems are designed to deliver better performance, lower power and smaller area, it also solves the fundamental problem of system yield and reliability.

I talked with Mr. Lee about Uniquify’s technology.

Wong: Why do DDR memory subsystems need to be fast and small?

Lee: First, let me explain why the DDR memory subsystem is important and relevant.

The DDR memory subsystem is ubiquitous in SoCs. Where there’s a CPU and the need for more system performance, there’s a memory interface. Because the DDR memory subsystem is typically the highest bandwidth bus in most systems, operating at multi-GHz data rates with read-write timing margins measured in picoseconds, system performance depends on the memory interface performance. This is the reason why DDR memory subsystems have to be fast to get the best system performance.

Small is what’s required for the consumer market application and cost is a driver. In order to get the cost down, the chip needs to be smaller.

Related Articles

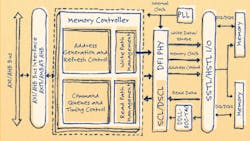

- Self-Calibrating Memory Controllers

- Achieve Reliability, Availability, And Serviceability For Memory Interfaces

Wong: Where did your inspiration come from?

Lee: My inspiration is my experience. I’ve worked with SoCs (or ASICs when I started) all my career and, what I didn’t experience, I learned from my friends. When a chip comes back from the foundry and packaging company, design teams do a bring up. Almost always, the DDR memory is the most troublesome when it comes to system yield and field reliability. If the DDR system does not work reliably, the product won’t work.

Before DDR, which came out around 2000, it was SDRAM memory, a bottleneck slowing down traffic to the chip, because of yield and reliability. There is zero tolerance in the memory interface for even single bit errors.

I discovered that the JEDEC standard was lacking in addressing some of these issues that real designers and companies were facing and I was determined to solve them. Even today, JEDEC has tried to address some of the issues, but doesn’t entirely.

Wong: Can you describe self-calibrating logic (SCL) DDR IP?

Lee: SCL is an efficient piece of logic for memory IP to precisely measure timing across the DDR system and automatically adjust it for each system. A system goes through many variations. Predicting variation beforehand is impossible –– it’s ludicrous to try. With SCL, the circuitry tests the memory parameters, such as timing, as the system is powered up. In other words, SCL caters to each system at production so that there is no more guessing or there is no more “one-size-fits-all” scheme. It understands each system’s parameters and sets the best possible set of parameters for that system.

Wong: And, what about dynamic self-calibrating logic (DSCL) DDR IP? What’s that?

Lee: Dynamic SCL builds on SCL by applying the same technique during system operation. A system’s operating parameters change as it runs, whether it’s temperature or voltage function. And as a result, timing parameters change, too. DSCL dynamically tunes the critical DDR timing continually during system operation. And, it’s not done just at power up, but continually. It measures how the behavior changes over time and adapts the system to accommodate those changes.

We’re the first memory IP provider to come up with a solution to this problem. Our cleverly considered improvement to DDR memory subsystem IP solves the fundamental problem of system yield and reliability and gives our customers the fastest DDR memory subsystem to better their system performance. Both SCL and DSCL are patented.

Wong: Are you seeing adoption of DDR4 memory? If so, any particular application?

Lee: Yes, many SoC engineering teams now are adopting DDR4. As an SoC engineering company, Uniquify has many customers and partners and we’re often able to determine usage trends. DDR4 was lagging a bit more than we expected. Of course, some leading-edge companies were moving to DDR4 and others were holding off. At the end of this year, we expect to see many more fabless semiconductor companies move to DDR4 in all kinds of applications.

Typically, we see a divide between SoC engineering teams that need to conserve power for handheld devices or smart tablets and high-performance designs, such as servers and conventional networking chips and set-top boxes. LPDDR (low-power DDR) is used for low-power applications, while DDR is used for high-performance design.

Wong: What about LPDDR4 memory?

Lee: We’ve been surprised to find designers going directly to LPDDR4 (the latest JEDEC standard) and skipping LPDDR3 for high-performance, low-power mobile applications. The LPDDR4 architecture was designed to be power neutral, offer 2X bandwidth performance over previous generations, with low pin-count and low cost. It’s also backward compatible.

Wong: What’s the outlook for memory IP in 2014?

Lee: We see a bright memory space that’s growing in 2014. A recent report shows that the semiconductor foundry sales are growing. That portends good things for memory IP since virtually all chips require a memory interface today. The CPU needs a DDR interface, and it has become the most popular IP in any chip. The market will grow in 2014. It typically grows from 15-20% yearly and I expect that number to be higher.

On the Uniquify front, we’re working with a partner now on revolutionary IP that goes beyond the existing JEDEC standards and making them even better.

About the Author

Josh Lee

President and CEO

Josh Lee is President and CEO of Uniquify in San Jose, California. With two cofounders, he bootstrapped Uniquify into what is now a thriving IP and chip design and manufacturing services business collectively referred to as “ideas2silicon.” Lee and the team also built a comprehensive design management system, Perseus, used to manage all SoC projects at Uniquify. He has gained more than 18 years’ of experience in the semiconductor industry through various technical and executive roles. Lee holds a Bachelor of Science degree in Electrical Engineering and Computer Sciences from the University of California, Berkeley, and a Master of Science degree in Electrical Engineering from Cambridge University in the United Kingdom.

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.