This article is part of TechXchange: RISC V

Download this article in PDF format.

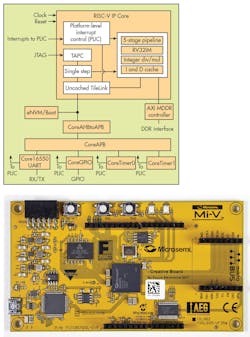

Many companies today are exploring free, open-source hardware and software as an alternative to closed, costly instruction set architectures (ISAs). RISC-V is a free, open, and extensible ISA that’s redefining the flexibility, scalability, extensibility, and modularity of chip designs (Fig. 1). Despite its rich ecosystem and growing number of real-world implementations, there are misconceptions about RISC-V that have companies holding back from fully realizing its benefits.

1. RISC-V is an open, free ISA enabling a new era of processor innovation through open standard collaboration.

Let’s take a closer look at several myths about the RISC-V ISA to better understand the technology, tools, and requirements of the architecture, and how it can be used to accelerate innovation and drive down costs.

1. RISC-V is another processor design.

RISC-V is a fixed ISA that’s open. Standard extensions can optionally be implemented, but the base ISA is frozen forever. Because the ISA is fixed, software need only be written once, and it runs forever on any RISC-V core. Innovation can be accelerated by leveraging the open ISA. Organizations are able to optimize and customize a design for their specific applications. RISC-V is to open hardware what Linux has been to open-source software.

2. RISC-V is purely for use in academia, not industry.

Numerous corporations are implementing RISC-V to monetize their cores. IP vendors such as Andes Technology, Codasip, Bluespec, and Cortus all offer RISC-V cores to be implemented in silicon. SiFive has both licensable IP cores as well as customizable silicon based on RISC-V, including a 32 bit RISC-V SoC available for sale today. Microsemi (Fig. 2), Rumble Development, and VectorBlox offer soft RISC-V cores that run in FPGAs. For example, at the fifth RISC-V conference on November 30, 2016, a full-production time-lapse camera was shown using a RISC-V core in an IGLOO2 FPGA.

2. Microsemi’s IGLOO2 FPGA features a RISC-V IP core.

3. There are no FPGA cores or integrated design environments that I can use to evaluate RISC-V.

Microsemi has taken the lead in this area, having both FPGAs that support RISC-V cores and an integrated development environment (IDE), SoftConsole, that supports development and debug of the RISC-V ISA on the company’s RTG4, IGLOO2, and PolarFire FPGAs. Virtual platforms (software simulation) are also valuable for evaluating RISC-V—Imperas has models of both the 32- and 64-bit RISC-V ISAs and an IDE (M*SDK) for software development, debug, and test on RISC-V. These models are also available through the Open Virtual Platforms website. In addition, to evaluate a RISC-V design, a prospective user could use the HiFive1 product from SiFive, a RISC-V-based, Arduino-compatible board.

4. RISC-V requires you to pay for a license to use it.

Anyone who wants to consume a RISC-V core can do so freely—there are no licensing fees to use the RISC-V ISA. For example, many soft RISC-V cores can be freely downloaded from the Microsemi GitHub site or others. For commercial end products, usage of the RISC-V trademark or the RISC-V logo is only permitted under the license granted within the RISC-V Foundation Membership Agreement. The key point is that the ISA has a permissive license.

5. Companies that build RISC-V cores have to share their IP with customers.

There are no grant-back requirements for any IP that implements the RISC-V ISA. Designers are free to develop proprietary implementations for commercial exploitation or open-source implementations to be shared as they see fit. The RISC-V Foundation encourages both types of implementations.

Also, some of the software tools supporting RISC-V include specific IP. Typically these tools, such as tools from Antmicro and Imperas, use a similar license to the Berkeley Software Distribution (BSD) license from the University of California, Berkeley; public release of the IP isn’t required.

6. RISC-V processors aren’t as fast or efficient compared to x86 or ARM processors.

Processor speed and efficiency depends entirely on the quality of the implementation, including microarchitectural design, circuit design, and the process technology used. Fundamentally, a RISC-V implementation should not be less efficient than x86 or ARM; in fact, the modularity of the RISC-V ISA design enables implementations to be more efficient than legacy ISAs such as x86 or ARM. Because the RISC-V ISA is open, everyone effectively has a microarchitecture license to implement the most optimized processor for their applications.

7. Software tools for RISC-V don’t exist.

RISC-V support was added to both the GNU/GCC and GNU/GDB toolchains in May 2017. Low Level Virtual Machine (LLVM) tools are also available through the RISC-V website. Both of these can be found on the RISC-V software tools page.

Antmicro has an Instruction Set Simulator (ISS) for RISC-V. QEMU also supports RISC-V with its ISS environment. Imperas has a full virtual platform-based software development environment with its M*SDK product. And Microsemi has its Eclipse-based SoftConsole IDE for RISC-V software development.

SiFive also offers a free, Eclipse-based IDE called Freedom Studio.

8. Multiple RISC-V cores can’t operate in the same design and they can’t operate with another processor.

RISC-V and other processor cores can behave similarly. For example, SiFive announced a multicore RISC-V solution featuring both 32- and 64-bit cores. RISC-V cores can run in-order or out-of-order operations. A RISC-V core is also used as a microcontroller with an Athena TeraFire cryptographic processor to provide advanced security features. The 32-bit RISC-V core is responsible for configuring the type of secure data communication that the TeraFire core will implement in a PolarFire FPGA.

9. It’s dangerous to trust a RISC-V core.

If the register transfer level (RTL) of an IP core is available and based on a well-known, open specification, it can be inspected and analyzed—a very important feature for design security. When using a soft RISC-V core for an FPGA, the entire RTL design can be reviewed to ensure that it’s secure. This simply isn’t possible with closed-processor architectures, whether they’re soft or hard processors. One could argue that this makes RISC-V much more secure than ARM or Intel cores, or any proprietary soft core where the RTL isn’t accessible.

10. There’s no Linux OS support for RISC-V.

On the contrary, several flavors of Linux are supported, including Yocto. Current RISC-V Linux development is based on the 4.6 version of the Linux kernel and the RISC-V patchset is on a good route for inclusion in the 4.14 kernel merge window. That means RISC-V will soon be a mainline platform in Linux. Unlike home-baked ISAs, the open and collaborative nature of the RISC-V ISA actually makes it easier for companies to coordinate their Linux and other OS support efforts, improving the software experience for everyone and driving down costs.

11. It’s impossible to port a RISC-V design from an FPGA to an ASIC.

Several IP vendors have emulation platforms that run on FPGAs. Codasip and SiFive both have FPGA prototypes of cores that can be ported to custom silicon. As an FPGA vendor, Microsemi provides the RTL for its RISC-V soft cores. With the RTL, it’s very straightforward to do a port to an ASIC and there’s no need to pay for IP licenses or royalties.

Moving past these 11 myths creates the opportunity for developers to realize all of the advantages RISC-V has to offer, benefiting the entire ecosystem. For more information, go to RISC-V Foundation or Microsemi RISC-V Information.

Ted Marena is Vice Chair of the RISC-V Marketing Committee, RISC-V Foundation, and director of FPGA/SoC marketing at Microsemi.