Improve Logic Timing with Worst-Case Analysis

Worst-case circuit analysis (WCCA) is a cost-effective means of screening a design to verify with a high degree of confidence that potential defects and deficiencies are identified and eliminated prior to test, production, and delivery and that the design will function, within specifications, throughout its lifetime. The digital worst-case timing analysis (WCTA) portion of WCCA analyzes the timing of digital devices and signal paths under worst-case conditions. It usually accompanies many other assessments such as decoupling, signal integrity, and dc compatibility.

For WCTA, TimingDesigner analyzes the results of the printed-circuit board (PCB) propagation delay, extracted from HyperLynx and the static timing numbers of the FPGA or ASIC. Through WCTA, setup and hold time violations can be analyzed.

This file type includes high resolution graphics and schematics when applicable.

Digital Worst-Case Timing Example

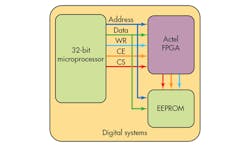

A portion of an actual analysis is shown below as an example of the WCTA of an EEPROM interface. In this design example, a 32-bit CPU microprocessor core drives control signals to a 4-Mbit EEPROM multichip module (512 × 8-bit) interface device and Actel FPGA (Fig. 1). The FPGA static timing data is derived from SmartTime software. The timing analysis is performed with HyperLynx and TimingDesigner.

For the WCTA of the EEPROM bus, two sequential read operations, two sequential write operations, a memory read followed by a memory write, and a memory write followed by a memory read all need to be verified. Also, the digital WCTA examines both rising and falling edges of the slow and fast cases for timing board propagation delay.

For this example, HyperLynx is used to measure the board propagation delay. The input to this software consists of the board design file, which includes the exact geometry of all traces, pads, and layer dimensions. The I/O models used vary based on the part type, availability of appropriate models from the manufacturer, and other factors. The board propagation delay is measured for the fast and slow corners. The fast/strong simulation corner is performed at the lowest temperature with the higher-power supply voltage. The slow/weak simulation is performed at the highest temperature with the lowest-power supply voltage.

The EEPROM requirements can be found in the vendor datasheet. For this example, the requirements of the write cycle are obtained from the Maxwell datasheet.1 The microprocessor requirement also can be found in the vendor datasheet. For this design example, the requirement of the write cycle is obtained from the Aeroflex datasheet.2

WCTA Process

The first step in the analysis is to set up the PCB file in HyperLynx to establish and confirm the physical properties of the various PCB stack-ups. Simulation calculations are made using post-layout models extracted from the HyperLynx design file. The second step is to set up and confirm the validity of all of the IBIS models. The third step is to measure the board propagation delay or the skew.

In most driver/receiver modeling cases, unless test data shows the necessity to do so, no additional degradation due to aging or radiation of any parameter is required. In other words, it is assumed that the end-of-life tolerance limits are the same as the beginning of life extreme limits, which include temperature (usually the military temperature range) and voltage (4.5 to 5.5 V or 3.0 to 3.6 V). This assumes that the application is not immersed in a radiation environment, such as a space application.

If radiation is present, then the performance of the components is either guaranteed to a certain total dose level or radiation degradation test data is required. Any degradation due to aging and radiation deltas are included in the parameter ranges. It also assumes that most of the variation in most driver/receiver parameters is due to parasitics that depend on fixed physical dimensions of elements and that the dimensions do not change significantly over life.

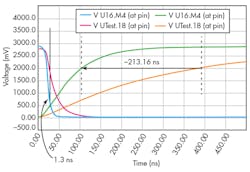

Finally, all of the delays are inserted into TimingDesigner, and the requirements are applied. The results of WCTA show if the EEPROM requirements are met under the stated conditions. Figure 2 shows the HyperLynx simulation for the fast corner and the propagation delay.

Due to the differences in loading, input thresholds, and trace lengths, the actual waveform at the receiver can be interpreted as a transition at a different time from the test load. The results of the simulation are a slow rise time delay of –233.16 ns and a slow fall time delay of 1.3 ns. These results become adjustment factors to the driver propagation delays as specified in the datasheet. These factors add to the specified propagation delays and affect the outcome of the analysis for each net or a functional group of nets in Timing Designer.

The duty cycle, period, and jitter can be included as properties when a clock signal is defined and can be adjusted at any time. The minimum pulse width of the write signal does not comply with the manufacturer specification limits under the worst-case condition (see the table). Also, the chip select signal is not ready at the first rising edge of the clock. Therefore, the chip select setup time requirement is not compliant under the worst-case condition. Once the WCTA is performed, though, it is easy to reanalyze and confirm compliance of the design.

Design issues can be easily identified via WCTA. Issues that cause data corruption, anomalous operation, and even product failure can be uncovered and fixed. The performance of such analyses creates many lessons learned for designers. Current designs are improved, and WCCA supports continuous improvement plans (CIPs), resulting in better future products and better engineers.

References

1. Maxwell Technologies, Microelectronics Downloads, www.maxwell.com/products/microelectronics/downloads

2. LEON 3FT Microprocessor, www.aeroflex.com/ams/pagesproduct/prods-hirel-leon.cfm

Sahar Sadeghi, senior engineering scientist, is a digital worst case and PDN analyst at AEi Systems LLC. She is interested in FPGA/ASIC design, design for testability and reliability, testing, and modeling. Also, she is responsible for evaluation of 3D power integrity software. She has experience in project management, design, and analysis of military and aerospace digital electronics. She earned her MBA in 2005 and master’s degree in electrical engineering in 2012.

Charles E. Hymowitz, managing director, is chair and CEO of AEi Systems LLC. Also, he was a cofounder of Intusoft and SalesMountain. He was the co-author and editor of SPICE Circuit Handbook, Simulating with SPICE, The SPICE Cookbook, Power Specialist’s App Note Book, and The SPICE Applications Handbook. He is a graduate of Rutgers University with a BS in electrical engineering as well as the Stanford University Executive Institute program for Management of High-Technology Companies. He can be reached at [email protected].

About the Author

Sahar Sadeghi

Senior Engineering Scientist

Sahar Sadeghi, senior engineering scientist, is a digital worst case and PDN analyst at AEi Systems LLC. She is interested in FPGA/ASIC design, design for testability and reliability, testing, and modeling. Also, she is responsible for evaluation of 3D power integrity software. She has experience in project management, design, and analysis of military and aerospace digital electronics. She earned her MBA in 2005 and master’s degree in electrical engineering in 2012.

Charles Hymowitz

Managing Director, Chair, and CEO

Charles E. Hymowitz, managing director, is chair and CEO of AEi Systems LLC. Also, he was a cofounder of Intusoft and SalesMountain. He was the co-author and editor of SPICE Circuit Handbook, Simulating with SPICE, The SPICE Cookbook, Power Specialist’s App Note Book, and The SPICE Applications Handbook. He is a graduate of Rutgers University with a BS in electrical engineering as well as the Stanford University Executive Institute program for Management of High-Technology Companies. He can be reached at [email protected].