Microchip’s 16-bit dsPIC family of microcontrollers offers efficient digital signal processing (DSP) using a modified Harvard bus architecture. Its instruction set and hardware are designed to deliver fast, deterministic performance. There’s support for three operand instructions and the dual-address generators allow for simultaneous access to memory in a single cycle.

So what could be better?

How about a pair of dsPICs in a single package? Enter the dsPIC33CH family. Each chip includes a 90-MIPS master core that can run from flash plus a 100-MIPS dsPIC33CH core that runs from ECC RAM. The two cores share a mailbox and FIFO interprocessor communication system; otherwise, the two are functionally isolated. Each maintains its own complement of memory and peripherals.

The dual-core dsPIC33CH architecture has two isolated cores with their own peripherals and memory. FIFOs and mailboxes provide processor-to-processor communication.

The 100-MHz processor cores have new instructions, as well as context-selected accumulators and status registers. This delivers almost double the performance of previous dsPICs for common algorithms such as a 3-pole 3-zero compensator. The new architecture also lowers system latency.

The master core features a peripheral complement more weighted toward communication with CAN-FD, a first for dsPIC33 chips, and multiple UART, SPI and I2C interfaces. The slave has a preponderance of analog support. The PWMs have 250-ps resolution as well as advanced timing-control features. The master includes 128 kB of ECC flash, while the slave executes out of 24 kB of ECC program RAM. The master has 16 kB of data RAM, while the slave has only 4 kB.

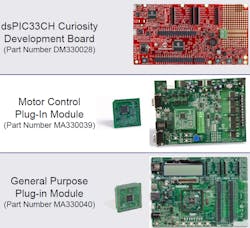

The dsPIC33CH Curiosity board includes click board interfaces (top). The Motor Control Plug-in Module works with the Microchip’s motor-control development boards (middle), while the general-purpose module can plug into the Explorer 16/32 development boards (bottom).

The dual-core system can address a range of applications, such as power management or motor control with motors running at speeds in excess of 100K RPM, and high torque at near-zero RPM for motor control in power tools. The slave can be dedicated to that task, or multiple motors can be controlled using both cores. The matching peripherals allow for easy migration of tasks between cores at the developer’s discretion.

Pricing starts at $2 in volume. Chips come in numerous form factors, from an 80-pin TQFP to a 28-pin SSOP or a tiny 36-pin, 5- by 5-mm UQFN package.

The dsPIC family is supported by the MPLAB X IDE as well as the MPLAB Code Configurator. There’s also a cloud-based MPLAB Xpress IDE for online development. Furthermore, developers can take advantage of the MPLAB XC16 optimizing compilers.