DPU ASIC Embraces 400G Ethernet

This video is part of TechXchange Talks.

What you’ll learn

- What is a DPU?

- What it takes to handle 400G Ethernet.

- Why an ASIC is needed to deliver high-performance, low-latency computing.

Data processing units (DPUs) are tightly integrated network front-end systems designed to offload network processing chores from the host. Sometimes referred to as SmartNICs or infrastructure processing units (IPUs), they’re essentially the internet-facing components for a cloud server system.

DPUs typically have a compute cluster that’s complemented with network interfaces and hardware accelerators to process network communication services such as authentication and encryption. Virtualization support is usually part of the mix to address cloud-based virtualization.

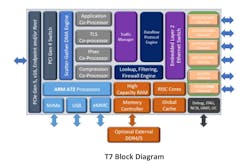

Chelsio Communications’ T7 ASIC can handle four 100G or one 400G Ethernet connection (Fig. 1). I talked with Bob Dugan, Director of Engineering, about the platform and the challenges addressed by a DPU (see the video above).

DPUs are needed to address high bandwidth throughput as well as manage data with support such as encryption at wire speeds. It also needs to minimize the latency between the incoming data and the host that eventually must process the massaged data. Host processors used to handle these chores with conventional network interface cards (NICs), but that’s impractical with today’s speeds looking to push past 400 Gb. TCP offload engines (TOEs) were just the start. This type of DPU provides even more functionality.

The T7 400-Gb support comes from 56-Gb PAM4 SERDES. The ASIC provides an x16 PCI Express (PCIe) interface to the host. This interface supports Unified RDMA including RDMA over Converged Ethernet v2 (RoCE) and iWARP. As a result, the DPU can handle traffic with minimal host intervention. The system is designed to provide zero-copy communication internally with kernel bypass without the need to rewrite applications.

PCIe functionality enables the ASIC to be a Root Complex and/or an End Point so that it can easily be an edge device or a front end to a server network. Versions of the chip are available with a built-in PCIe switch and an Ethernet switch.

The chip can handle storage applications, providing compression and encryption support for SSD drives. It can also manage native NVMe-to-NVMe and NVMe-to-Ethernet bridging as well as storage protocols, such as different RAID levels.

The T7 is compatible with the prior versions, such as the T6 found on the T62100-CR adapter (Fig. 2). The T6 has an x16 PCIe Gen 3 interface and handles two 100G Ethernet ports. Like the T7, the T6 is software compatible with prior versions of the platform.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.