The Quartus II FPGA design tool just got a boost from Altera. It incorporates the new SpectraQ engine which is designed to handle large and complex applications as chips are being delivered with over 5 million logic elements (LEs). The chips often include hard CPU and GPU cores. Timing closure is a significant issue as it is on large ASICs (see “Network-on-Chip Gets Automated Timing Closure”) where a signal cannot traverse a chip in a single-clock cycle.

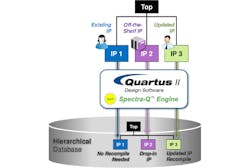

One way Quartus II is streamlining the design process is by using a hierarchical database (Fig. 1). This allows the SpectraQ to incrementally update a design. The approach is becoming increasingly important as more third-party IP is used as well as addressing large designs that are usually broken into smaller modules. In the past, the entire system would be recompiled if even small changes were made.

The SpectraQ engine contains a number of fine-grain stages for addressing various design and layout aspects down to routing and timing closure. It supports incremental changes that can greatly speed up the design cycle for large projects.

The SpectraQ engine provides a platform for other development tools like the model-based DSP Builder. There is also support for OpenCL programs. Altera supported this feature earlier (see “How to Put OpenCL into an FPGA”), but the current incarnation builds on the common SpectraQ platform. This approach was also used for the A++ Compiler for HLS system. This is a GNU C++/C that allows conversion of applications to FPGA definitions. Like the OpenCL support, the A++ Compiler for HLS (high level synthesis) can be configured via directives to optimize the conversion.

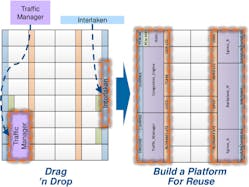

Another new feature is the ability to drag-and-drop major components in the design tool, allowing generation of an initial floor plan layout very quickly. Blocks like an Interlaken interface, traffic manager, or DDR memory controller interface can be placed, but there are limitations that the system takes into account so that a placed block will work properly (Fig. 2). The advantage of the Blueprint Platform Designer is that the pinout for a project is known at the start and designers know that this part of the design will work since it has already been verified. These software conversion tools can significantly speed up creation of FPGA applications.

Changing the underlying system in Quartus II allowed Altera designers to make performance changes. The system now leverages multicore processors and compute farms. Being able to utilize more compute power is significant for very large projects. The incremental support also helps for these types of projects since the amount of work that needs to be done when changes occur is significantly smaller than recompiling the entire system.

This latest version of Quartus II, v15.0, comes with new IP. This includes support for the Hybrid Memory Cube (see “Hybrid Memory Cube Shows New Direction for High-Performance Storage”) and HDMI 2.0 MegaCores. There are IP improvements as well. The updated JESD204B core operates at 9.255 Gbit/s on the Arria V FPGA and 5 Gbit/s on the Cyclone V.