COMPANY OVERVIEW

About Arteris IP

Contact

More Info on Arteris IP

Arteris is a leading provider of system IP for the acceleration of system-on-chip (SoC) development across today’s electronic systems. Arteris network-on-chip (NoC) interconnect IP and SoC integration technology enables SoC creation success with proven flexibility and ease for a variety of applications and markets including AI, automotive, communications, consumer electronics, enterprise computing, and industrial. Arteris technology ensures higher product performance with lower power consumption and faster time to market, delivering better SoC economics for its global customer base including semiconductor manufacturers, OEMs, hyperscale system houses, semiconductor design houses and other producers of electronic systems.

The Arteris product line is silicon-proven, supporting SoC innovation from creation to integration.

Network-on-Chip IP Products

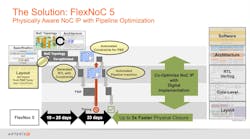

- Non-coherent NoC IP, with FlexNoC and FlexWay

- Cache-coherent NoC IP, with Ncore

- Last-level Cache, with CodaCache

SoC Integration Products

- SoC integration with Magillem Connectivity, Magillem Registers, and CSRCompiler