Different test strategies and methods at wafer probe and package test are needed to accommodate today�s burgeoning SIP technology.

The consumerization of the electronics markets continues its rapid pace. According to a December 2004 report from the research firm iSuppli, the mobile communicationsg, consumer electronics, and automotive integrated circuit (IC) markets will account for 42.3% of total semiconductor revenue in 2005, with a value in excess of $100B.

A requirement for portability in these markets drives the need for lower voltage processes on the logic side along with more efficient analog, memory, and RF processes. System-in-a-package (SIP) technology is being adapted to help reduce the size of end-use devices such as mobile phones, personal digital assistants (PDAs), and digital cameras while increasing system power efficiency, ruggedness, and signal integrity. This shift to integrating analog and RF IC technologies with logic and memory ICs in a SIP allows smaller end-use devices with lower overall system current draw at price points demanded by these markets.

What Is a SIP?

SIPs contain multiple heterogeneous and homogenous ICs along with passives and, in some cases such as automotive applications, microelectromechanical systems (MEMS) packaged together in planar, stacked, or combination topology (Figure 1). The IC types range from dynamic RAM (DRAM) to digital signal processor (DSP) and system-on-a-chip (SOC) including analog and RF. The ICs can be bare dice or packaged parts that then are integrated into the SIP. When bare dice are integrated into a SIP, they adversely affect yield and will require different test strategies at wafer than those used for dice in individual packages.

For SIPs, tests deployed at wafer will provide a known quality die (KQD) to the SIP integrator. The delivery of KQD adds another requirement for IC component suppliers since they now must provide the SIP integrator with a breakdown on what has and has not been tested and the outgoing defect rates. The SIP integrator then can determine if further testing is needed to achieve the quality target for the intended market balanced against the costs of testing, scrapped material, and effort.

Innovations in ATE Platforms

As the use of KQD in consumer markets replaces the use of known good die (KGD) used in military/aerospace applications, manufacturers now require new ATE innovations and advanced test techniques to improve wafer test effectiveness.

One example of innovation is the shift to supplying single scalable platforms. Today, ATE suppliers offer platforms that scale digital pin-count, digital speed, and analog and RF test capabilities. The single scalable-platform concept ensures upgradability, allowing test capability to match the volumes and test requirements of the product mix including bare die and package.

For individually packaged dice, the costs of ATE for wafer probe can range from one-half to one-third the cost of ATE for packaged functional test. For new designs or IC processes that are ramping into production for a SIP project, meeting the KQD requirements may require upfront test capabilities at wafer probe similar to those typically used for package test.

Once the design has fully ramped or the IC process has stabilized, the test deployed will have excess capability, resulting in unnecessary additional cost of test. Given the cost-competitive markets these ICs and SIPs are used for, cost of test is a key variable. To bring the cost of test back in line for a given die requires additional platform innovations.

An original approach is a flexible performance library that supports per-pin licensing of digital vector speed and depth that floats to given tester pin or tester in the enterprise. This allows very specific channels or classes of die to be targeted, providing a level of digital performance that would be too expensive to deploy widely across all tester pins and die tested.

A base level of performance and cost of test can be established for given classes of die. Any tester in the enterprise can be reconfigured easily and economically using software licensing, via the performance library, for die test requiring higher digital performance, including speed and vector memory.

Improving Test Methods

There are two basic approaches to producing dice of high known quality. The obvious approach is to move the final tests, normally done on packaged parts, to the wafer probe stage. This, however, is challenging due to the lower signal- and power-integrity connection usually provided by a probe compared to a socket. Final test also usually relies on the direct measurement of the functional specifications.

One alternative is to detect the same defects found by the package tests with indirect tests that do not require the high signal-integrity connection or expensive instruments of the package test. This approach is called defect-based testing (DBT).

The most widely used DBT method is quiescent power supply current (IDDQ). IDDQ is a DC measurement that relies on simpler connections and instruments than at-speed testing. It can replace at-speed scan or functional testing to a reasonable quality level because digital logic speed failures often are caused by resistive bridging or capacitively coupled open defects which also elevate IDDQ.

Since IDDQ is a parametric measurement, unlike the pass/fail nature of most digital tests, it also detects latent or reliability defects that may not cause a failure until later in the product�s life. Normal field-effect transistor (FET) off-leakage rises in comparison to defect current with process shrinks. As a result, it�s mandatory to measure IDDQ at multiple vectors and perform signal processing to extract the defect signal out of the background noise.

With the IDDQ method, defects result in unexpected values called outliers. Expected process variation causes the main distribution in Case 1 of Figure 2.

click here to see larger image

When using deep submicron (DSM) technologies, fault-free and faulty IDDQ distributions overlap due to FET off-current increasing faster than on-current, creating a current measurement dynamic range problem (Case 3 of Figure 2). The pass/fail overlap in Case 3 requires changing the sequence from marking the dice as good/bad in the test flow to testing enough dice on the wafer to find a pattern and then making fault-free/fault decisions.

With this IDDQ method, signal processing and contrasting conditions are used for pattern recognition and to establish fault-free/fault limits. This requires a large number of measurements and calculations.

To determine a distribution within a die, a vector pattern is repeated to establish an IDDQ max/min ratio. Die-to-die vector comparison also can be executed by calculating figures of merit such as nearest neighbor residuals (NNR) in which the mean or median IDDQ of neighboring dice is used to estimate the center die IDDQ and neighbor current ratios (NCR) where the ratio of IDDQ for one die is compared to that of its neighbor.

For fault-free dice, the ratio should approach one for the same vector. The use of wafer spatial patterns looks for high-frequency spatial variations, which indicate a faulty die.

These IDDQ methods, in turn, continue to drive precision current measurements on the ATE system. This requires a low-noise ATE architecture with high-resolution device power supplies (DPS) that have fast IDDQ measurement capabilities to meet the throughput requirements for the increasing number of IDDQ measurements.

Soon a cell-phone SIP could include baseband circuitry, media processors, and memories manufactured in a 90-nm process. According to failure-analysis experts, digital yield-loss dominance is shifting from hard failures, primarily stuck-at faults, to parametric failures, primarily path-delay and transition-time faults. Capturing these increasingly common timing faults may require testing at-speed.

As more IC designs are targeted for SIPs and portable applications, the output drivers are no longer required to drive the capacitance of a signal path that includes propagating the signal onto a PCB and then to a receiver. A test mode for the output driver is required so that it can drive the signal to the ATE pin. At the same time, to screen these delay and edge-rate faults, the ATE must have the necessary edge placement accuracy (EPA) and rise times at the die contact points.

Enhanced Voltage Stress and IDDQ

All defect-based tests including IDDQ are indirectly related to conventional functional or structural tests. For that reason, it is beneficial to stress the defects to increase their effects on the circuit-under-test by accelerated aging. Stress makes both initial and latent defects easier to detect.

Most semiconductor defects are accelerated by a combination of temperature and voltage. Since probing at high temperature is difficult and temperature acceleration is slow, requiring hours of stress time, temperature stressing is most practically done on packaged parts in separate burn-in ovens. This is not practical for producing good dice for SIPs.

In contrast, voltage stress can easily be applied by probes, assuming a high voltage can be applied without causing destructive breakdown. It is possible to accelerate many defects at probe.

Voltage stress is especially effective for identifying bridging defects. This entails operating the circuit in many logic states to apply voltages across multiple pairs of nets, especially in the interconnect, which in turn requires the part to be clocked. Since the defects to be stressed are the same ones whose quiescent current is to be measured, the IDDQ vectors also are the best stress vectors.

The easiest way to apply this stress is to raise the constant power supply and input voltages. In today�s nanometer processes, the voltage required to highly accelerate interconnect defects will cause a toggling FET to break down destructively. Fortunately, a metal-oxide semiconductor field-effect transistor�s (MOSFET) drain-to-source breakdown voltage is higher when it is off than when it is on. When static, every FET in a complementary metal-oxide semiconductor (CMOS) gate is in series with an off-FET, which will handle the stress voltage.

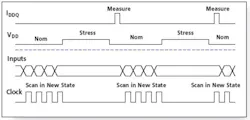

This led to the development of what IBM calls enhanced voltage screen (EVS), which replaces the older dynamic voltage screen (DVS). The sequence, as shown in Figure 3, is to clock in a pattern at nominal voltage, stop the clock, bump the supply to the stress voltage and hold it for a period, return the supply to its nominal voltage, measure IDDQ, and proceed to the next pattern.

At the end of the vector set, the IDDQ measurements can be analyzed for a signature that determines if the part contains a defect. Depending on which signatures have been found useful for a given product, IDDQ also may be measured at the stress voltage or before the stress bump.

SIP Package Test

Once the SIP integrator has packaged all the passives, KQD, and known good memory, some level of package test must be performed to ensure the targeted ppm defects are not exceeded. If defects are found only in the package interconnect, then this might be a simple system-level test.

The packaging process, however, may create defects in the dice, which then would require testing the internals of the affected dice. Package test also may be required to verify that the performance tolerances of the chips and package accumulate in such a way that the resulting system performance is within targeted specifications.

When the defect rates out of wafer probe exceed the target-system defect rate, more test coverage will be required at package. The package test will most likely contain some level of at-speed functional digital test as well as RF and analog and memory tests to capture any false positive die or packaging defects.

Test modules created for the die parts can be leveraged into the package test flow as long as a common platform is used at both wafer probe and package test. Package test ranges from simple interconnect system test to comprehensive DC, scan, at-speed functional, analog, RF, and memory test.

Conclusion

The growth in the use of SIPs, driven mainly by the price-sensitive wireless, consumer, and automotive markets, is requiring a shift from KGD to KQD. As a result, different test strategies and methods at wafer probe and package test are being deployed. To meet these requirements cost effectively, the ATE platform and its underlying architecture must support a wide range of test and reliability screening methods to support the large disparities in test times and resource utilization across the range of dice integrated into an SIP.

Reference

Sabade, S.S. and Walker, D.M., �IDDX-Based Test Methods: A Survey,� ACM Transactions on Design Automation of Electronic Systems, Texas A&M University, Vol. 9, No. 2, April 2004, pp.159�198.

About the Authors

Peter O�Neill is a research engineer in the Semiconductor Test Group at Agilent Labs. He received a B.S.E.E. and an M.S.E.E. from Purdue University and then was employed by Hewlett-Packard where he worked in process, devices, SPICE modeling, and reliability engineering. Shortly after Agilent�s spin-off from HP, Mr. O�Neill joined the central labs to work on IC test. Agilent Technologies, 970-288-4562, e-mail: [email protected]

Tom Vana is a solution product manager for SOC test systems at Agilent Technologies. In 20 years at the company, Mr. Vana has held positions in field applications, market development, and product management for semiconductor test and the electronics functional-test market. Agilent Technologies Automated Test Group, 408-553-3342, e-mail: tom_vana@ agilent.com

For more information

on the performance library

www.rsleads.com/504ee-200

April 2005

About the Author

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: