Explore the many options available today for developing advanced, processor-intensive HIL applications.

With new technologies such as PCI eXtensions for Instrumentation (PXI), open graphical development and simulation software, and the availability of a wide range of hardware with support for real-time operating systems (RTOSs), engineers and integrators now have more options for developing advanced, processor-intensive HIL applications.

Traditionally, aerospace and automotive design engineers have implemented HIL prototyping systems because of the need for advanced suitability before full-scale development. Software design models for new products are deterministically simulated at high speeds and interfaced with input and output signals from hardware I/O in real time. The result is better designed products and less iteration with costly prototypes.

In the case of aerospace design, where the cost of the prototype often is secondary to safety concerns, HIL system prototyping is a necessity. With the availability of suitable commercial technologies, a new demand is being satisfied for cost-effective implementation of very flexible, high-performance HIL applications. The capability to integrate multivendor technology and use off-the-shelf components saves time and costs, increases system performance, and reduces maintenance considerations.

In one application, Averna Technologies created a new fly-by-wire data acquisition and simulation system for the Aerospace Division of Thales Canada. Thales is an international electronics and systems group serving the defense, aerospace, services, and security markets.

The HIL simulation platform will be used to test electronic flight control systems that are used to provide additional stability, pilot assistance and relief, and flight support during the entire flight schedule. Averna�s solution is based on PXI, an open, multivendor industry standard.

HIL Test-System Requirements

To test the fly-by-wire system, the HIL setup required hundreds of channels of analog and digital I/O, ARINC-429 for avionics communications, and IRIG-B for overall system synchronization. Some of the analog signals would be inputs from transducer sources and require signal conditioning.

The system had to acquire data at a high sample rate to capture any transients and have less than 10-�s latency to update I/O output within a 1-kHz loop rate. A single development environment was needed to create the data acquisition program, which required compatibility with The MathWorks Simulink� device model simulations and synchronization between systems with less than 1-�s timing errors.

Delivery was required within five months. In traditional custom-designed systems, this level of performance under tight time and budgetary constraints would be difficult.

System Design

In addition to the requirement for hundreds of channels of I/O with ex-pandability to 2,000, the system required integration of 64 channels of ARINC-429 communications. The ARINC-429 specification defines a unidirectional, differential, twisted-pair data bus used to transfer bipolar return-to-zero (BPRZ) avionics data at either 12.5 or 100 kb/s.

The unidirectional nature of the system and lack of shared bus access mean that many wires can be required in a large airplane. In its favor, ARINC-429 provides high-reliability data communications.

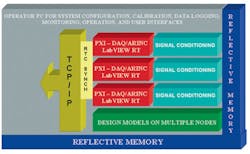

Distribution of simulation tasks over several processors in the system necessitated sharing information with low latency and high throughput. Each PXI chassis has a reflective memory module housed in a CompactPCI carrier board. Reflective memory transmits data from a simulation model or a data acquisition system to all other clients of the HIL system with throughput approaching several tens of megabytes per second with less than a 1-�s delay.

The Inter Range Instrumentation Group (IRIG) standard was developed by the U.S. Department of Defense for modern communications, missile, and telemetry applications that require time synchronization information. Of the many IRIG formats, the most common version is IRIG-B, which uses a 1-kHz frequency to encode the date, hour, minute, and second.

Specifically, the IRIG-B 74-b serial time code contains 30 b of binary coded decimal (BCD) time of year data, 17 b of straight binary seconds of day, 9 b for year information, and 18 b for control data. One word is transmitted per second using an amplitude-modulated 1-kHz carrier to provide 10-ms resolution. Alternatively, modified Manchester encoding providing 1-ms resolution can be used.

Selecting the Hardware Platform

Based on performance, communications, and expandability requirements, Averna identified three key factors used to select the hardware platform:

1. Availability of embedded real-time controllers.

2. Availability of analog I/O, digital I/O, ARINC-429, reflective memory, and IRIG-B modules.

3. Need for an open, multivendor industry standard.

Based on these criteria, ARINC-429 modules from Condor Engineering were selected because of their performance, channel density, and RTOS driver support. GE Fanuc supplied an ultrahigh-speed reflective memory system that communicated among modules via fiber-optic links.

Suitable off-the-shelf commercial hardware was not available for PXI clock-to-IRIG-B synchronization. Averna used LabVIEW to develop custom field-programmable gate array (FPGA) code for an NI PXI-7831R-reconfigurable FPGA module that generates the IRIG-B signal to synchronize the ARINC-429 transceiver modules with the PXI clock.

Also, additional signal-conditioning hardware was designed to amplify, provide isolation, and simplify synchronization of a variety of avionics signals generated from custom LVDT and RVDT transducers. The conditioned signals are wired to I/O modules in two PXI chassis.

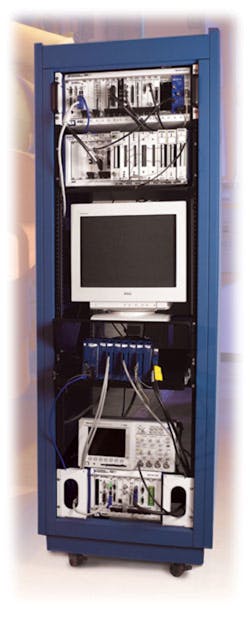

The PXI platform provides modularity and system scalability along with precise timing, synchronization, and distribution of a real-time clock. The time-critical code running in real time on a PXI embedded controller handshakes with the signal-conditioning hardware and deterministically acquires input signals and updates outputs on the same clock edge (Figure 1).

Software Considerations

Considering the range of I/O, system performance, and RTOS requirements, Averna identified three main criteria to select the development environment.

1. Graphical development environment.

2. Real-time support for a broad range of PXI hardware.

3. Open software platform with Simulink compatibility.

With a deadline of five months and tight budgetary constraints, Averna Technologies selected LabVIEW to decrease development time, provide real-time support, and offer compatibility with existing Simulink models.

To perform the necessary simulation calculations, multiple commercial desktop controllers were used to run the Simulink device models. Reflective memory was used to share data between the device model simulations and the HIL system with less than 250 ns of latency.

A LabVIEW-developed custom command interpreter provides remote CPU interrupt and procedure-invocation capabilities through reflective memory. The application supplies system configuration of tag names, hardware channels, acquisition rates, and system calibration. Data is displayed in real time to multiple system operators for immediate feedback and then transferred to remote computers for post-processing, analysis, and storage.

Conclusions

The current PXI system is scalable to thousands of channels by adding more PXI chassis. This expansion has been tested and is not expected to impact performance. Thanks to the range of hardware and the fact that PXI is an open industry standard, Averna incorporated a wide range of hardware with an RTOS and delivered a complete HIL test system to Thales on time and under budget.

LabVIEW offered three main advantages that made implementing this system easier: the ease of use of a graphical development environment, support for real-time RTOS capabilities, and open software compatible with Simulink models. The fly-by-wire HIL test system saved more than $200k in implementation costs and several months of development time.

About the Authors

Robert Jackson is a PXI product manager at National Instruments where his current projects include the PXI chassis. He joined the NI staff in 2002 and holds a B.S. in chemical engineering from Oklahoma State University. National Instruments, 11500 N. Mopac Expressway, Austin, TX 78759, 512-683-5440, e-mail: [email protected]

Shahzad Sarwar, Ph.D., is director of industrial and real-time solutions at Averna Technologies. He has a doctorate in electrical engineering from University of Rome and 17 years of experience in R&D, measurement automation, simulation, and control systems. Dr. Sarwar has authored more than 100 publications in various international journals. Averna Technologies, 275 Slater St., Suite 900, Ottawa ON K1P 5H9, 613-230-0283, e-mail: [email protected]

June 2005