PCI Express (PCIe) is the next-generation peripheral bus for industrial computing. It provides a scaleable, high-bandwidth, point-to-point pathway between peripheral cards and the computing core while retaining application software compatibility with previous generations. For machine-vision systems, the capabilities of PCIe already are yielding increased frame rates and simplifying the implementation of multichannel capability.

PCIe emerged as a solution to the increasing mismatch between the PC�s peripheral card bus and the I/O demands of high-performance graphics, communications, and storage. A typical 32-b, 33-MHz PCI system only offers a 132-MB/s data rate, yet the PCI bus could not significantly increase clock speed or bit width because of cost and skew across the parallel bus.

The PCI bus topped out at a data rate of 528 MB/s with a 64-b, 66-MHz specification. PCI-X, an enhancement to the PCI bus, proved both complex and costly to implement, typically achieved no more than 1-GB/s bus bandwidth, and only supported three to four cards on the bus.

The PCI Special Interest Group solved these limitations by creating PCIe, which eliminates the skew and fan-out limitations of high-speed parallel buses by adopting a serial bus structure. Even though PCIe uses a serial connection at the physical layer, it retains backward compatibility with traditional PCI peripherals at the driver, operating system, and application levels.

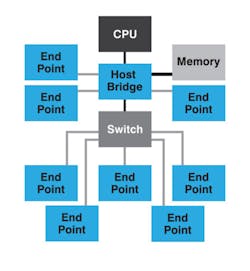

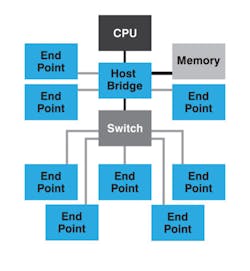

PCIe provides a scaleable, high-bandwidth bus structure. Using a switch matrix, the serial PCIe bus makes its connections point-to-point to provide a direct, bidirectional link between the two communicating entities (Figure 1). From one to 32 lanes can be used in a PCIe connection, supplying data rates as great as 8 GB/s in each direction. The recently introduced PCIe 2.0 specification doubles the achievable data rate, and higher link rates are in development.

PCIe provides PC-based system developers with several advantages. One is an increased capability to balance cost and performance. Designers only need to use as many lanes as their performance requirements dictate.

The bus�s dedicated connection also helps eliminate system bottlenecks. The bandwidth of the PCI bus had to be shared among all the peripherals and other system functions so that the available bandwidth decreased with each additional peripheral.

PCIe data transfers do not need to share bandwidth. In addition, the peer-to-peer capability allows multiple transactions to occur simultaneously if a nonblocking switch is used and lets peripheral devices stream data direct to system memory without CPU intervention.

The Right Design Approach

The design of a peripheral card for a PCIe system can use either a bridge or a native interface. Because of software compatibility, it is possible to connect an existing PCI or PCI-X design to a PCIe slot through a bridge chip. This approach offers a low-cost upgrade path to the new bus structure but results in a design that is limited to the performance that the original bus interface provided.

Simply using a bridge chip to upgrade a design runs into system initialization issues. During allocation of system resources, some BIOS software has difficulty reaching through a bridge to determine card resource requirements. This leaves system developers with a need to check the compatibility of motherboard BIOS and card bridge chip to avoid problems.

Making PCIe the peripheral card�s native interface eliminates the need to check for compatibility since there is no bridge device to confuse the BIOS. A native PCIe design also allows the card to offer maximum performance. Without the restriction of the PCI interface, the card�s hardware can fully use the bandwidth of the PCIe link as well as directly access a 64-b full memory space.

Adopting a native PCIe interface provides the maximum degree of motherboard compatibility, freeing the system design from artificial limitations. The one-lane designs offer the greatest flexibility because one-lane cards will work in any PCIe slot in any motherboard. For higher performance, four-lane designs are suitable for use in conjunction with workstation and server-grade motherboards, which typically offer four- and eight-lane card slots.

Powering High-Speed Image Capture

Because of their native PCIe interface, the speed and dedicated bandwidth available to DALSA�s frame-grabber boards enable users to address a wider variety of machine vision applications than was achievable using PCI devices. One application area that benefits is the use of high-speed image capture for analysis of dynamic systems. An example of this application type comes from the Low-Speed Wind Tunnel in Braunschweig (NWB) operated by German�Dutch Windtunnels (DNW).

The DNW-NWB sought to test the typical trajectories of objects jettisoned from transport aircraft. Wind conditions around the aircraft can cause the boxes to tumble and even move upwards, potentially striking and damaging the aircraft (Figure 2). The DNW-NWB wanted to use the data to validate and refine its airflow simulation software.

Figure 2. Objects Jettisoned From Aircraft

To perform these tests, the DNW-NWB developed the Stereo Metric Tracking System to determine the 3-D movement of boxes with differing weights falling from the aircraft. Dual high-speed cameras and frame grabbers captured images of the falling boxes, acting as the eyes of a vision system that used the two images to reconstruct the 3-D coordinates of each box. Three markers on each side of the boxes provided reference points to help identify the location and orientation of each box.

The performance needs of the Stereo Metric Tracking System were high. Two Mikrotron MC1310 Cameras captured images of 1,280 x 1,024 pixels at 500 frames/s. This required a system capable of feeding a data rate of 655 Mpixels/s from each camera to its corresponding frame grabber. To meet this need, the DNW-NWB selected DALSA�s Xcelera Frame Grabbers that handle a data rate to 1 GB/s both on input and output over its four-lane PCIe interface.

To process the image data and extract the 3-D position, the frame grabbers ran DALSA�s Sapera LT Image Processing Software along with user-supplied analysis software. The user software, picColor from FIBUS, handled the 3-D position extraction and trajectory tracking. Once the system extracted and stored the tracking data, it discarded the images.

The backward compatibility of PCIe was particularly important to this project because it was an upgrade effort of a proven system. Earlier versions of the system depended on 64-b PCI-X boards for image capture and processing.

The high-performance demands and the need to share bus bandwidth between the two camera views pushed this design to its limits. By converting to PCIe, the DNW-NWB increased system performance to provide substantial margin for growth.

Converging Multiple Views

Multicamera metrology is another application area that benefits from PCIe�s attributes. Such systems examine objects from several directions simultaneously, inspecting all surfaces without manipulating the object.

A conventional PCI-based system that offers multiple image-capture channels must share the system bandwidth among the channels. This sharing quickly becomes a bottleneck, lowering throughput of the inspection system.

A PCIe-based system can use multiple frame grabber boards and provide each with an independent link to system memory. Because the bandwidth of a PCIe link is dedicated to the data transfer it carries, each frame grabber in the system can operate at its full speed without affecting the others. This, in turn, allows the inspection system to provide maximum throughput.

A multicamera system in use at a manufacturing facility in Asia provides operators with simultaneous views of objects at different locations on the production line. Each view presents its own type and amount of information about the process, examining objects that may vary in length from a few millimeters to several meters. From these views, the operator can make measurements at numerous points within the process.

The manufacturer wanted the visualization tasks to be handled by the frame grabber without CPU intervention and did not want the host system performance to be compromised by the imaging tasks. The manufacturer chose DALSA�s Bandit3 Frame Grabber, which offers image capture and display capability using a one-lane PCIe interface.

By choosing the PCIe bus for its frame-grabber selection, the manufacturer preserved system bandwidth for other operations. While a PCI frame grabber would have to share the system�s bus capacity, using a PCIe frame grabber provided a 250-MB/s channel for displaying the images while leaving the 132-MB/s PCI bus free for other uses. The result was an increase in system performance over previous generations.

In addition to freeing PCI bus capacity, the frame grabber freed motherboard card slot resources. Because the PCIe bus offers such high bandwidth, the system could be implemented using a one-lane PCIe slot. This preserved the motherboard�s 16-lane slot as well as PCI-32 slots for control operations. By reducing the required motherboard resources, choosing PCIe for the frame grabber interface allowed the manufacturer to use a smaller, more compact PC as the host system.

The compatibility of PCIe with the existing PCI infrastructure also is a major advantage. The operating system sees the frame grabber as just another VGA adapter. As a result, the manufacturer�s software, which relied heavily on standard display application programming interface (API) commands, worked without any modifications.

Future Trends

Additional features of PCIe can enhance future machine vision systems. The bidirectional capability of the bus, for instance, can help simplify the use of coprocessors to enhance system performance.

Gigabit Ethernet cameras have been making inroads into general-purpose machine vision applications, increasing the need to offload from the host CPU the task of converting the GigE Vision packets into usable images. A Bayer color GigE camera sending data at 100 MB/s, for example, would require the host computer to spend tremendous amounts of valuable CPU clock cycles simply converting and decoding images into usable formats.

The CPU can be off-loaded by using a general-purpose coprocessing board and a network interface card (NIC) on the PCIe bus and the bidirectional capability of the bus. The camera sends its data to the network, and the NIC forwards the data to the coprocessor across PCIe.

The coprocessor performs both packet conversion and Bayer decoding in real time, then streams the data to system memory using the transmit half of its PCIe link. This high-speed data transmission, processing, and storage can all occur without CPU intervention, enabling it to perform more critical analysis. This approach also allows standardized PCIe coprocessor cards to be used rather than the proprietary mezzanine cards in PCI systems, simplifying system design and lowering cost.

This kind of growth potential along with the current benefits of PCIe will ensure its adoption in many coming generations of PCs. Its attributes applied to machine vision systems will, in turn, allow these systems to provide greater throughput and multichannel capabilities unattainable using the PCI bus. This growth in performance is essential for keeping pace with the increasing demand for machine vision in manufacturing.

Machine vision systems make it possible to inspect parts and components at every stage of the assembly process. This, in turn, prevents the accumulation of errors that previously were discovered only at the end of the process.

This capability to reduce waste and improve efficiency will ensure that machine vision plays an ever-more important role in business. Embracing PCIe technology will provide developers with design options that ensure maximum performance in future generations of vision-enabled industrial computers.

About the Author

Inder Kohli is a product line manager at DALSA Digital Imaging and based in St. Laurent, Quebec. He holds a bachelor of commerce with honors from the University of Delhi in India and a certificate in management information systems from McGill University as well as a diploma in electrical engineering. Before joining DALSA in 1994, Mr. Kohli worked as an application support engineer, a software product manager, and an automation technologist. DALSA Digital Imaging, 514-333-1301, e-mail: [email protected]

May 2007

About the Author

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: