The Open Coherent Accelerator Processor Interface (OpenCAPI), announced at this week's Flash Memory Summit, is managed by the OpenCAPI Consortium. It’s a new high-performance bus interface designed for servers that now has memory semantics in the form of the Open Memory Interface (OMI). The big difference between it and the standard memory interfaces for DRAM is the switch from parallel to serial in the same fashion that PCI Express (PCIe) replaces the parallel PCI bus. The consortium was started by AMD, Google, IBM, Mellanox Technologies, and Micron.

Last year, IBM announced that new Power9 processors would incorporate an OpenCAPI interface for memory support. It will be interesting to see if other processor and GPU vendors follow this route, but the advantages are similar to those of PCIe.

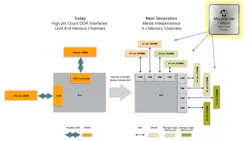

Microchip is at the forefront of delivering on storage needs. The SMC 1000 8x25G PM8596 chip acts a front end to memory using an OMI interface (Fig. 1). One big difference between the conventional parallel interface and the serial OMI is that the interface is platform agnostic. OMI has an abstraction layer; therefore, a controller can attach to different types of media.

1. The SMC 1000 8x25G chip supports DDR4 DRAM memory while providing a standard OMI serial interface.

The typical DDR4-3200 memory channel requires over 300 pins and has a bandwidth of 25 GB/s. A single OMI memory channel uses about 75 pins and can deliver the same 25-GB/s throughput. The 4x OMI system employs about the same number of pins as the parallel interface, but it has a 100-GB/s bandwidth or an increase of a factor of four.

Microchip’s SMC 1000 8x25G controller chip supports x4 and x8 interfaces with 25.6-Gb/s serial links using OIF-28G-MR support. This includes dynamic low-power modes. Housed in a 17- by 17-mm package, it can interface to NVDIMM-N persistent-memory modules as well as a range of 16-Gb DDR4 memory with up to four ranks. The on-board, open-source firmware handles DDR/OMI initialization and provides in-band temperature and error monitoring support as well as support for the ChipLink GUI.

The SMC 1000 8x25G provides security and data-protection services, too. It can support hardware root-of-trust, secure boot, and secure update. Also included is single-symbol-correction/double-symbol-detection ECC support. The chip can handle memory scrubbing with auto correction of errors.

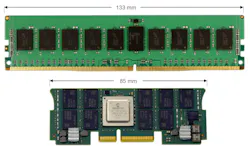

The DDIMM form factor (Fig. 2) provides a point-to-point 8x25G OMI memory interface. These DDIMMs support DDR4 DRAM memory. DDIMM modules are available from a number of vendors, including SMART Modular, Samsung Electronics, and Micron, in multiple capacities from 16 GB up to 256 GB.

2. This DDIMM form factor is designed to support a range of volatile and non-volatile storage chips.

Using the OMI approach brings advantages with it, such as higher bandwidth and lower pin counts. Normally, load/store operations are queued by the memory controller within the processor. In this case, the memory controller is integrated within the SMC 1000 8x25G. Microchip’s product has innovated in the area of device latency, so that the difference in latency between the older parallel DDR interface and this newer OMI serial interface is under 4 ns when compared to LRDIMM latency.

The OpenCAPI consortium has made the host and target OMI IP component technology available to consortium members on a royalty-free basis. This should further adoption, as will processor, GPU, and FPGA implementations that take advantage of it. Likewise, embedded applications could be ripe for this type of interface, especially single-channel implementations where reduced pin count would be advantageous. Computing on the edge is demanding more, higher-performance memory.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: