MIPS has its sights set on high-performance applications like 5G with its midrange MIPS I7200 architecture. The platform introduces the nanoMIPS instruction set, which is designed to be more space-efficient. MIPS I7200 only runs nanoMIPS code, so applications originally targeted for other MIPS platforms will need to be recompiled.

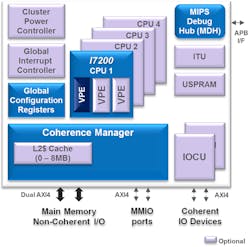

1. The midrange MIPS I7200 targets high-performance applications like 5G. Each core has three virtual processing elements (VPEs).

The multicore cluster (Fig. 1) has four cores that each incorporate three virtual processing elements (VPEs). Prior MIPS platforms had two VPEs per core. The system incorporates an enhanced coherence manager (CM) to handle the 8 MB of L2 cache. The CM reduces the latency of the L2 cache by two to six cycles. It works in conjunction with up to two IO Coherence Units (IOCUs). The Cluster Power Controller (CPC) supports clock gating per core and handles voltage and gating for each core.

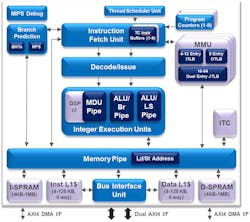

The cores (Fig. 2) are built around a nine-stage, dual-issue, in-order pipeline with vertical multithreading (VMT) support. Each of the three VPEs appear as logical cores to the operating system. The system supports either a 32-region memory protection unit (MPU) or a full virtual memory management unit (MMU) with translation lookaside buffers (TLBs). Thanks to the MMU, operating systems like Linux can run on the I7200, while the MPU support will allow an RTOS to handle real-time chores with the required memory predictability. This approach provides developers with a more flexible design and implementation options.

2. The MIPS I7200 core has a nine-stage, dual-issue, in-order pipeline with vertical multithreading (VMT) support. It supports MMU or MPU memory management.

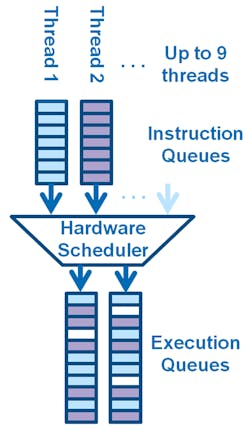

The system supports up to nine threads total that feed the dual-issue execution queues in the VMT architecture (Fig. 3). The threads can be allocated to the three VPEs in any combination. This architecture provides a 50% performance gain for a 20% silicon footprint increase compared to the previous generation. The system allows threads to be “parked” while waiting for a high priority event. Thus, the event handler can start immediately without a context switch. The instruction queues for a parked thread are already filled when an event occurs.

The system provides deterministic operation when used with the MPU. It also unifies tightly coupled scratchpad RAM (SPRAM) for instruction and data. These can be shared within a core or across multiple cores.

3. The VMT support is built around a deterministic, dual-issue scheduler that’s fed by up to nine threads.

The more compact nanoMIPS instruction set architecture (ISA) allows more instructions to be packed into SPRAM or instruction caches. The new ISA eliminates branch delay slots found in the original MIPS instruction sets, and the 32-bit instructions implement the most commonly used instruction sequences into single operation. The ISA is source-code-compatible with the existing MIPS ISAs; it’s sort of a RISCy/CISCy mix with variable-length 16-, 32- and 48-bit instructions.

Many SoCs combine different cores to provide OS and RTOS support, leading to more complex systems and related programming support. The MIPS I7200 provides this type of flexibility with a single architecture. A system built using TSMC 16FF+ delivers over 40,000 EEMBC CoreMarks at 1.7 GHz, with each core using only 150 mW. The IP is available from MIPS and is supported by foundries like TSMC, Global Foundries and UMC.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.