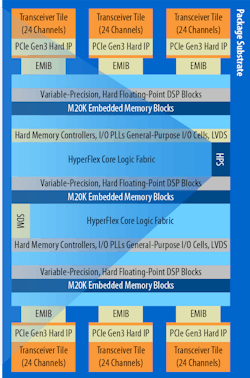

Intel’s Stratix 10 FPGA family utilizes 14-nm transistor technology and heterogeneous 3D system-in-package (SiP) integration (Fig. 1) to combine different silicon technologies in the same package. It uses embedded multi-die interconnect bridge (EMIB) technology to link multiple die.

The platform targets applications like network function virtualization (NFV), data center acceleration, software defined radio and 5G wireless communication.

1. Intel’s Stratix 10 utilizes heterogeneous 3D system-in-package (SiP) integration with embedded multi-die interconnect bridge (EMIB) technology to link multiple die.

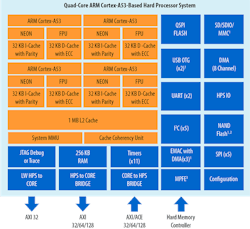

The new Stratix 10 SX family of systems-on-a-chip (SoCs) provides over one million logic elements (MLE) and integrates 1.5-GHz quad-core Arm Cortex-A53 MPCore support (Fig. 2). Versions are available with up to 5.5 MLE. The system employs Intel’s HyperFlex core fabric architecture to tie the components together. The SoC allows high-speed data-plane processing via the FPGA fabric, while the MPCore manages the control plane.

The HPS architecture implemented with the Stratix 10 incorporates a system memory management unit (SMMU) that enables hardware virtualization across the processor and FPGA domains. The family also supports a cache coherency unit (CCU) to provide one-way I/O cache coherency with the Cortex-A53 MPCore.

2. The Stratix 10 SX incorporates 1.5-GHz quad-core Arm Cortex-A53 MP support.

The FPGA fabric can include up to 10 TFLOPS of hardened, floating-point DSP blocks in addition to the embedded high-speed transceivers, hard memory controllers, and protocol intellectual-property (IP) controllers. The systems include a x8 PCI Express Gen 3 interface and three Ethernet MACs. There’s also 10/40G BaseKR- forward error correction (FEC) hardware support.

Additional hard logic includes AES-256/SHA-256 encryption/authentication support, a physically unclonable function (PUF), ECDSA 256/384 boot-code authentication, multi-factor key infrastructure with layered hierarchy for root of trust, and side-channel attack protection. A Secure Device Manager (SDM) handles updates of FPGA configuration code.

The Intel Quartus Prime Design software works with the DSP Builder for Intel FPGAs and Intel HLS Compiler for FPGA designs. The Intel SoC EDS, intended for software development, enables customers to utilize the Arm Development Studio 5 (DS-5) Intel SoC FPGA Edition to create and debug software applications. Developers can also take advantage of OpenCL support for the FPGA fabric using Intel’s OpenCL FPGA compiler technology.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.