Accurate Test Without ATE-Generated Vectors

A unique opportunity to address SOC accuracy vs. cost of test challenges comes with the development of BIST Assist 6.4 by Agilent Technologies. When integrated into Agilent�s 93000 Series SOC Tester, a BIST Assist board allows four high-speed serial interfaces to be fully exercised on DUTs at speeds up to 6.4 Gb/s.

Although consumer demand for faster and more sophisticated electronic products has driven economic growth, it also has highlighted the cost-of-test dilemma. Large and complex SOCs often are at the heart of consumer products, which means that regardless of their advanced technical capabilities, the devices must have a low cost.

Many variations of built-in self test (BIST) have been applied to test the internal operation of a DUT, resulting in lower production costs. A major remaining problem has been comprehensive testing of fast serial interfaces such as PCI Express, Serial ATA, FibreChannel, and Serial RapidIO. These high-speed links will become commonplace as the convergence of computing, communications, and audio and video entertainment moves forward.

Recognizing that cost of test is an important issue, designers already have applied BIST techniques to the serial I/O ports. Generally, the device manufacturer has the option of using conventional ATE to apply bit patterns with a wide range of amplitude and timing control or BIST-generated patterns in a loop-back configuration with fixed amplitude and timing. The first approach is accurate and slow; the second is fast but only guarantees performance at a single operating point.

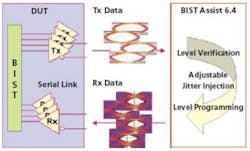

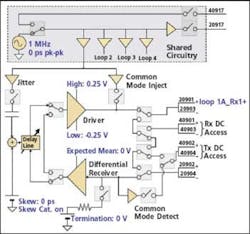

BIST Assist hardware is inserted in the loop as shown in Figure 1. Control software supports variable signal amplitude and delay so that operation is verified with all allowable values. Further, known amounts of impairments such as jitter, skew, and common-mode signals may be injected to ensure correct DUT behavior under less than optimum conditions. Figure 2 is a detailed block diagram of one channel.

Figure 1. BIST Assist Hardware Inserted in Loopback Signal Path

Figure 2. Detailed Block Diagram of One BIST Assist Channel

For each of the four separate differential loops on a BIST Assist board, hardware specifications include a data rate from 1.5 to 6.4 Gb/s, 100-mV input sensitivity into a 100-W load, and a 1.8-Vpk-pk differential receiver range. Jitter may be applied at a 10-kHz to 100-MHz rate from either an onboard sine wave generator or an external source with an amplitude of up to 430 ps.

Common-mode signals can be detected at levels from -1 V to 3 V and over a frequency range from DC to 100 MHz. The common-mode signal-injection level into an open circuit is 400-mVpk-pk. DC access provisions allow a DC signal, typically available from elsewhere in the test head, to be applied to the DUT.

Complementing the hardware features is BIST Assist work center software, which presents a GUI designed for setup and debug of loop parameters. Additional graphics utilities support the generation of shmoo plots with jitter tolerance performance diagrams dynamically tracking the effect of programmed loop parameter changes as they occur.

A few years ago, some industry pundits predicted that ATE prices would have to increase to $5M or $10M or more to test the complex parts forecast at that time. Instead, BIST, other DFT techniques, and serial links have been developed, which changed the test landscape.

Now, Agilent is offering a comprehensive PCI Express ATE system for $995,000 that provides 64 pins at 6.4 Gb/s and up to 256 digital pins at 400 Mb/s as well as the software, support, and services necessary to complete the solution. BIST Assist runs on 93000 SOC Testers using Rel. 4.3 HP-UX 11 or higher or Linux operating systems. Target DUTs must support loopback/BIST test mode.

About the Author

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: