Custom Blocks—The Key Ingredients for Embedded FPGA Success

Standalone FPGAs have been the mainstay for configurable, high-performance designs. Lately, integration with CPUs has been done from the perspective of including Cortex-A9s to help control the FPGA to augmenting a CPU, as with Intel’s latest Xeon/FPGA combinations.

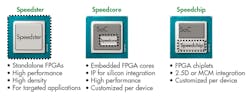

Achronix’s Speedster line has provided high-speed FPGA support for a while now. Developers can still take advantage of these standalone FPGAs, but the Speedcore and Speedchip embedded FPGAs (eFPGA) bring with them new development options (Fig. 1). Speedster FPGAs are available with TSMC’s 16-nm technology, and 7-nm support is expected in 2018. These FPGAs can have over two million lookup tables (LUTs).

Speedcore adds FPGA support within a system-on-chip (SoC). Speedchip provides similar support, but employs a 2.5D or multichip module (MCM) that links an SoC and an FPGA using interposer-style technology.

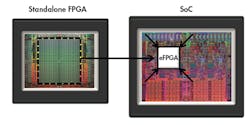

Designers can use Speedcore to embed FPGAs inside high-performance ASICs (Fig. 2). This provides a level of hardware configurability that’s not possible with a software-only solution. There are still many myths about embedded FPGAs—e.g., they’re expensive—but these have been debunked. Likewise, Speedchip isn’t the only embedded FPGA solution on the market. There are even standard chips, like Cirrus Logic’s PSoC series, that have FPGA-style, configurable logic.

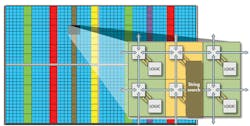

There are a variety of reasons for embedding an FPGA in an SoC but one of the more interesting ones is to reduce the overhead associated with interfaces. This can be significant, especially for high-speed serial interfaces that absorb almost half of the FPGA’s footprint (Fig. 3). Achronix’s Speedchip with custom blocks can further reduce an embedded FPGA’s footprint by almost 75%. This has the added advantage of reducing power requirements and even increasing performance.

A Custom Fit

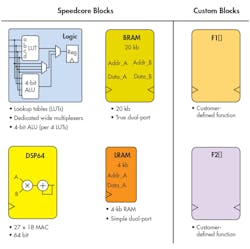

What differentiates Speedchip is the addition of custom-block columns within the usual FPGA fabric (Fig. 4). The bulk of an FPGA remains LUTs and the interconnect fabric associated with linking LUTs and other blocks together. Custom blocks contain logic that’s appropriate for a particular application, from packet processing to machine learning. Achronix can incorporate any number of different custom-block types depending on the application.

There are some considerations when designing custom blocks. For example, the custom blocks need to be sized based on the other standard blocks within the FPGA fabric. Custom-block sizes are usually some multiple of the LUT block that tends to be the smallest within the fabric.

Designers of Speedchip eFPGAs can take advantage of standard blocks as well as include one or more types of custom blocks (Fig. 5). Unlike a standard FPGA, an eFPGA needn’t include features like DSP support if that’s not required by the application. Adding the custom blocks to a fabric is actually easy, since they’re attached to the FPGA routing fabric in the same fashion as standard blocks. Of course, this means it will limit the number of connections, but this will be taken into account during custom-block design.

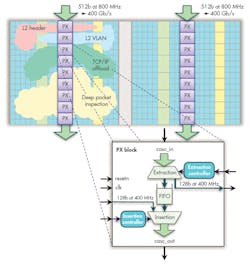

Achronix works with customers to determine the optimal design of a custom block and how it can be utilized. Standard blocks can be enhanced; for instance, by including more or less memory of various types. Likewise, how custom blocks interact can be different than how standard blocks work. For example, a packet-extraction (PX) custom block can provide a dataflow through PX blocks in a column in addition to the FPGA’s interconnect fabric (Fig. 6).

The advantage of using this type of dataflow is twofold. First, it doesn’t require use of the FPGA interconnect, which would be less efficient for this type of application. Second, the data can move at a significantly faster rate. In this case, it allows real-time processing of 400-Gb/s traffic by an 800-MHz FPGA. The FPGA provides control-processing logic, but this can operate at a slower rate. That may still push the limits of the FPGA fabric; however, the fabric would be incapable of handing this amount of data in real time.

Not all applications can fit this configuration, so it’s possible to have other configurations. For this reason, eFPGA designs require a tight relationship between the eFPGA vendor and the SoC designers. In addition, a significant number of design considerations have to be examined, from the type and complexity of the custom blocks to the amount of logic that can and should be placed into the conventional portions of the FPGA.

The amount of headroom provided in an eFPGA design is another consideration, since the FPGA fabric and standard blocks are still less efficient than hard logic either in a custom block or in the rest of the SoC. Providing more eFPGA support makes it possible to handle future changes or features, but this comes with a number of tradeoffs, including power and footprint overhead. It’s the usual embedded-design balancing act.

Tool Time

Achronix’s standard ACE design tools are employed with an eFGPA. This is important for two reasons. First, it means that designers have a single tool to work with that doesn’t change when custom blocks or layouts are used in their design. Second, it means that exposing an eFPGA to a customer’s design is possible without having a customer providing tool support.

Whether this exposure is appropriate will depend on a number of factors, but it could prove to be useful. For example, a custom SoC design may include an eFPGA that could then be configured for an end user’s application. Still, most designs will have very specific targets and will utilize the eFPGA to provide customization for a particular application. The eFPGA allows features like over-the-air (OTA) updates that would reconfigure the eFPGA.

In addition to ACE, Achronix provides a GUI application for the creation of custom blocks. Its Floorplanner tool aims at design optimization, making regional or site assignments for all block instances. Developers have access to ACE’s SnapShot embedded logic analyzer that can create complex triggers and show run-time signals within a Speedcore-based SoC.

Embedded FPGAs are changing the way ASICs are designed. ASICs had to deliver support that would not change over time. This is no longer the case, but the amount of configurability remains a design challenge that should not be taken lightly. Nonetheless, it can provide a significant edge in a very competitive market.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: