Automate Motor Control with a Smart FPGA

This article is part of TechXchange: RISC V

Lattice Semiconductor is well-known for its FPGAs. Usually, developers add their own firmware, but the company’s new Lattice Automate provides a more complete solution that incorporates artificial intelligence/machine learning (AI/ML) with motor control.

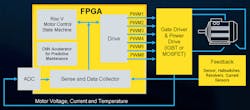

Lattice Automate targets a range of Lattice FPGAs with a framework that includes a soft-core RISC-V processor, a convolutional-neural-network (CNN) accelerator, and motor control along with Ethernet support (Fig. 1). The system can utilize any number of feedback systems like Hall-effect or current sensors. It also can work in a sensorless environment.

Likewise, Lattice Automate is able to control multiple motors using different drive systems. Included are predictive-maintenance models and application code that can be customized and extended. A host-based, GUI-based interface is available for system monitoring and control.

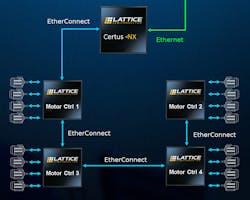

More complex systems require distributed motor control. Lattice’s EtherConnect technology is designed to connect multiple FPGAs using low-overhead Ethernet-style communication (Fig. 2). The connections can be done in a daisy-chain fashion as well as star configurations. The protocol and signaling is essentially the same but allows non-standard interfaces to be employed.

The real-time communication offers a way to synchronize motor control across the network. Protocol stacks are supplied for the RISC-V core. In addition, a conventional Ethernet interface can be included to provide a gateway.

Lattice’s FPGAs implement a hardware root-of-trust that can be taken advantage of by the RISC-V core. In terms of system configuration, Lattice Propel v2.0 allows a developer to combine features at a block level instead of the more precise, though detailed, Lattice Diamond. The latter is used to create blocks for Propel and provide logic-level design capabilities.

Many processor-based motor-control solutions exist, but Lattice’s approach is more efficient. It’s also possible to handle more and varied motors with an FPGA.

The reference design provided as part of Lattice Automate uses a single CNN accelerator per chip. It also supports TensorFlow Lite. Data collection support is in the mix, too.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: