Small-Form-Factor FPGA Packs a Punch

Lattice Semiconductor’s CertusPro-NX pushes the high end of the Nexus product line (Fig. 1). It’s built on the Nexus FDSOI transistor technology that provides high performance with low-power requirements. Competing products use up to 4X the amount of power for the same performance as the new family. The chips come in packages as small as 9 × 9 mm.

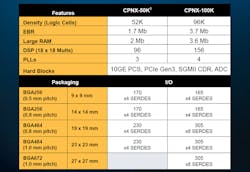

Up to 100K logic cells fit into these chip packages, along with SERDES that run at speeds up to 10.3 Gb/s/lane (Fig. 2). Thanks to the multiprotocol physical coding sublayer (PCS), the chips can handle protocols like PCI Express (PCIe) Gen 3 and 10 G Ethernet.

The FPGAs feature large and small internal memory blocks designed for low-latency operation. The chips also support LPDDR4 external memory. Large amounts of on-chip memory are included to meet the changing needs of designers. Likewise, the DSP support has been enhanced to work with machine-learning (ML) applications.

Lattice targets rugged and safety-critical applications with these FPGAs—the chips have an operating temperature range from −40 to 125°C. Their soft error rate is significantly better than the competition. The smallest package limits the number of SERDES and I/O but not the number of logic cells (Fig. 3).

Software support for the CertusPro-NX includes the new Radiant 3.0 development tool. SERDES analysis has been enhanced so that the chip can handle the higher-bandwidth SERDES. Other enhancements in this new version include better signal traceability throughout the design flow, with graphical feedback showing signal traces between the HDL source and RTL view.

This version of Radiant supports two synthesis engines: the Lattice Synthesis Engine (LSE) and the Synplify Pro synthesis engine. The same timing constraints and timing analysis are utilized by both. Timing analysis now runs independently of other operations, providing significant speed benefits and improving an iterative design process—changes need only run timing analysis, mapping, and place-and-route when required. Overall, new Radiant 3.0 features reduce runtime by 15% while delivering a 7% increase in design performance.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: