Lattice Semiconductor’s CrossLinkPlus is designed to handle interface conversion, including support for MIPI virtual channels (Fig. 1). The chip will be useful to bridge between a peripheral’s interface and one available on a host.

1. CrossLinkPlus wraps hard MIPI interfaces around a 6K LUT flash-based FPGA.

FPGAs have been used for this function since the onset of their development. The big difference tends to be the amount of hardened interfaces that are included with the FGPA. The alternative is to use a soft interface built using the FPGA fabric. There’s also the issue of PHYs that can be built-in or off-chip. Integrating hard interfaces and PHYs on-chip reduces the footprint, but it limits the chip to supporting the hard interfaces. On the plus side, the latest interfaces like MIPI D-PHY are becoming more readily available on hosts and devices.

CrossLinkPlus FPGAs come in a compact 3.5- × 3.5-mm package. They also consume less than 300 µW of power. Including hard interfaces on-chip makes this small, low-power solution possible while handling MIPI interface speeds up to 6 Gb/s.

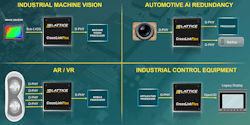

A range of interfaces are supported, including MIPI D-PHY, sub-LVDS, and OpenLDI (Fig. 2). The chip can handle one-to-one transitions for those interfaces that support individual channels. It can also manage multiple channels when using MIPI virtual-channel support. This allows a host to handle multiple MIPI-based input devices using a single MIPI interface or drive multiple devices, again, with a single MIPI interface.

2. CrossLinkPlus can handle interface conversion in addition to muxing/demuxing of MIPI channels and virtual channels.

The FPGA allows the data flowing through chip to be modified. The Lattice Diamond FGPA development software can take advantage of existing IP, as well as be used to create custom IP for the FPGA fabric. The flash-based FPGA allows for fast startup. The chip also features GPIO and I2C/SPI interfaces.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: