Split/Lock-Equipped Cortex-A76E Eyes Autonomous Vehicles

Arm processors are found in almost all autonomous vehicles these days in one form or another. They might be lock-step Cortex-R processors handling real-time control chores, Cortex-M microcontrollers working on sensors, or higher-end Cortex-A processors for command, control, and telematics.

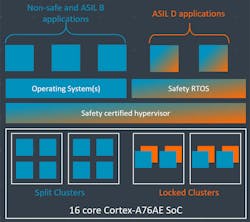

The 64-bit Cortex-A76 is the company’s new flagship processor that addresses everything from smartphones to servers. The latest addition is the Cortex-A76E that will find its way into autonomous-vehicle designs. It carries the Split/Lock architecture, which is found in the Cortex-R, on over to high-end SoCs (Fig. 1).

1. The Cortex-A76AE aims at safety-critical automotive applications with a split/lock mode that allows separation of cores into isolated groups as well as support lock-step mode between pairs of cores.

The Split/Lock support allows multiple cores to be split into separate groups with control over a set of peripherals. The Lock mode allows a pair of cores to be linked in lock-step mode for redundant, safety-critical applications. This has typically been employed in control systems such as brake-by-wire or other areas where failure isn’t an option, or at least not a desirable condition.

The ability to manage how cores are grouped will be a boon to SoC usage within many applications, not just automotive. It provides hardware isolation that’s initiated at boot time before applications are running. Many existing systems have forced partitioning, but that makes the systems less flexible. The new architecture means field updates can change how cores are distributed. It also makes much more sense to overprovision to anticipate future updates or deliver feature enhancements.

The splitting of cores at this level is different than managing multiple cores by a hypervisor. In the latter case, hardware still manages the isolation into virtual-machine partitions. However, this can be changed dynamically while the system is running. It’s actually quite useful, but makes it much more difficult to certify because the boundaries can be easily changed.

Likewise, hypervisor partitioning allows for allocation of peripherals. Again, though, this is a software-managed construct that uses hardware support to limit virtual-machine access to allocated peripherals. It’s even possible to create virtual peripherals that are then managed by the hypervisor or another virtual machine. Arm’s hardware split support forces the hardware into a configuration so that changes can’t be made by the software, even the hypervisor. This is necessary to guarantee that the designed and certified configurations are the only ones that will run on the system.

In the past, this isolation was done by using separate chips with fixed connections. This required custom configurations per application whereas the new approach allows more generic SoCs to be employed in a wide range of environments where each has its own configuration that can be verified. This level of support is needed for ASIL D applications. It’s useful for other applications, but mandatory for certified systems.

Other goodies come with the Cortex-A76AE announcement, too. It’s designed for clusters with up to 64 cores. In addition, it supports a scalable mesh network for on-chip connectivity; the cores include ARM V8.2 reliability, availability, and support (RAS) features. The RAS specification addresses error handling and recovery including features like error synchronization barriers.

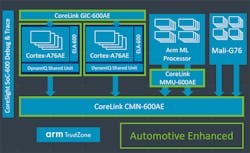

The Cortex-A76AE is designed to coexist with ARM’s machine-learning (ML) cores and neural-network (NN) accelerators (Fig. 2). This is key as the Cortex-A76AE cores will be managing and running ML applications for handling the array of sensor inputs from around an autonomous vehicle.

2. The Cortex-A76AE can coexist with ARM’s Mali graphics in addition to machine-learning cores and neural-network accelerators.

The ability to put more functionality into a single chip will be important in reducing power and the bill of materials (BOM) for systems that are becoming more complex. The approach improves the ability of developers to detect and manage errors while simplifying software that will run into billions of lines of code for autonomous vehicles. It’s likely to be more complex than even avionic systems, where safety concerns have been the highest. Part of the problem is that automotive environments are actually more difficult for computers to address than aircraft that have fewer obstacles to contend with and are used in more controlled environments.

The added level of safety and management comes at a cost, but Arm is looking to deliver power-efficient designs. A typical 16-core Cortex-A76AE system with CMN-600AE done using 7-nm technology will use less than 25 W while being suitable for ISO26262 ASIL D certification.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: