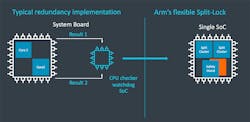

Arm has had lockstep cores since its Cortex-R family, which targets safety applications such as automotive where redundancy is important. Even FPGAs have incorporated hard-core Cortex-R processors. Earlier, the company announced that its Cortex-A76E for automotive applications included a feature called split-lock that allows developers to select how cores operate together or are separated. This approach makes it possible to consolidate multiple chips into a single SoC while providing the same level of safety assurance (Fig. 1).

1. Integrating multiple processors into a single SoC that still meets safety standards can be accomplished with Arm’s split-lock support.

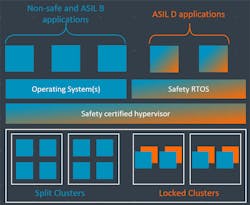

Arm’s latest automotive-enhanced (AE) processing core is the Cortex-A65AE. It features the split-lock support provided by the Cortex-A76AE, which allows a designer to configure a mix of isolated clusters, including dual cores in lockstep mode (Fig. 2). These SoCs can meet ASIL-D and ISO 26262 requirements needed for advanced driver-assistance systems (ADAS) and self-driving cars.

2. Split-lock allows a system to be configured at runtime. Clusters can be isolated by hardware and locked clusters provide redundancy as prescribed by designers.

The Cortex-A65AE targets 7-nm silicon and delivers multithreaded support. It’s designed to manage high-speed input from a large number of sensors such as LiDAR, radar, and visible infrared and thermal cameras. The cores can be integrated with Arm’s machine-learning (ML) accelerators.

Like the Cortex-A76AE, the Cortex-A65AE memory protection’s support includes single error correction, double error detection (SECDED) ECC and parity protection in the L1 cache, and SECDED ECC protection with the ability to correct errors in-line for the L2 and L3 caches.

Likewise, the Cortex-A65AE supports the reliability, availability, and serviceability (RAS) specification of the ARM 8.2 extensions. This includes standard error reporting across the core and the DynamIQ Shared Unit (DSU). It supports error injection for testing fault management as well as data poisoning to check deferring error aborts till point of execution. The entire AE platform is supported by the Arm Safety Ready program.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: