Automotive-Grade IP for 22FDX Process Focus of Joint Effort

Synopsys and Globalfoundries (GF) have announced a collaboration to develop a portfolio of automotive Grade 1 temperature (−40 to +150°C junction) DesignWare Foundation, Analog, and Interface IP for the GF 22-nm fully-depleted silicon-on-insulator (22FDX) process.

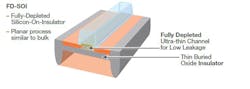

The 22FDX 22-nm platform targets connected and low-power embedded applications, delivering FinFET-like performance and energy-efficiency at the cost of 28-nm planar technologies, including up to 70% lower power than 28 nm, according to GF. The company’s 22-nm FD-SOI technology is utilized in a fab in Dresden, Germany and an upcoming fab in Chengdu, China.

The growth of safety features in today’s automotive systems-on-a-chip (SoCs) requires IP providers to put strict processes in place to help ensure that the IP meets stringent functional safety and reliability standards. Synopsys says that its silicon-proven IP meets the required automotive standards to help designers accelerate the qualification processes for their safety-critical advanced driver-assistance systems (ADAS), connected-vehicle and infotainment SoCs, as well as mainstream MCUs.

Globalfoundries’ 22FDX 22-nm FD-SOI (fully-depleted silicon-on-insulator) process technology platform targets connected and low-power embedded applications.

By providing IP that’s designed for high-temperature operation on 22FDX, Synopsys says it enables designers to reduce their design effort and accelerate AEC-Q100 qualification of SoCs for automotive applications such as e-Mobility, 5G connectivity, ADAS, and infotainment. The Synopsys DesignWare IP implements additional automotive design rules for the GF 22FDX process to meet stringent reliability and operation requirements, the company reports.

Not Their First Collaboration

Synopsys and GF have a long history of collaboration dating back to 180 nm. Currently, Synopsys provides a portfolio of DesignWare IP solutions for GF process technologies ranging from 130 nm to 12 nm. The IP solutions comprise logic libraries, embedded memories, embedded test and repair, analog IP, and wired and wireless interface IP. In particular, Synopsys and GF have collaborated on the development of Synopsys DesignWare Memory Compilers and one-time-programmable non-volatile memory (OTP NVM).

DesignWare Interface PHY IP, embedded memories, and logic libraries have been designed in accordance to Synopsys’ automotive mission profile following automotive-specific design rules. Synopsys says it verifies the IP with high-reliability automotive parts-per-million (PPM) targets and critical specifications according to automotive Process Capability Index (Cpk) distributions.

Cpk is an index—a number—that measures how close a process is running to its specification limits, relative to the natural variability of the process. The larger the index, the less likely it is that any item will be outside the specs.

This latest collaboration adds to Synopsys’ portfolio of automotive-grade IP that provides ISO 26262 ASIL B Ready or ASIL D Ready certification, AEC-Q100 testing, and quality management.

As a founding member of GF’s FDXcelerator Partner Program, Synopsys has collaborated with GF to develop an ecosystem that enables designers to deploy Synopsys’ RTL-to-GSDII solutions with attractive power and performance metrics for mobile and IoT designs on GF’s 22nm FD-SOI (22FDX) process. In parallel, Synopsys has also enabled the Synopsys Design Platform and developed DesignWare IP for GF’s 14- and 12-nm FinFET processes.

“GF’s close, collaborative relationships with leading automotive suppliers and ecosystem partners such as Synopsys have enabled advanced process technology solutions for a broad range of driving system applications,” says Mark Ireland, vice president of ecosystem partnerships at GF. “The combination of our 22FDX process with Synopsys’ DesignWare IP enables our mutual customers to speed the development and certification of their automotive SoCs, while meeting their performance, power, and area targets.”

Adds John Koeter, vice president of marketing for IP at Synopsys, “Our close collaboration with GF mitigates risks for designers integrating DesignWare Foundation, Analog, and Interface IP into low-power, high-performance automotive SoCs on the 22FDX process.”

At Mobile World Congress 2019 last week, Synopsys joined the GF NEXTech Lab Theater Session "Intelligent Connectivity for a Data-Driven Future" as part of a panel discussion with leading industry experts, including Joachim Kunkel, general manager of the Solutions Group at Synopsys, and Mike Cadigan, senior vice president of global sales, business development, customer and design engineering at GF. They discussed the importance of intelligent connectivity; the growth, demands, and innovations it’s poised to bring; and its impact across the semiconductor value chain.

About the Author

Murray Slovick

Contributing Editor

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: