Date & Time

- This webinar is now available On-Demand.

- Please complete the registration.

Event Type

- On-Demand Webinar

Speakers

Heidi Barnes

Senior Application Engineer

Keysight Technologies

Al Neves

Chief Technologist

Wild River Technology

Jack Carrel

Applications Engineer

Xilinx

Description

Why this webcast is important:

SerDes design engineers often find themselves confronted with channels that prove quite difficult to optimize. “It is all about the margins”.

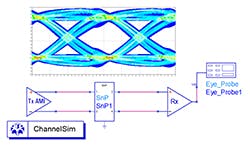

This webcast introduces a forensic channel analysis approach that implements both measurement hardware and EDA tools with contemporary SERDES internal tools (e.g., internal eye scan) for the purpose of optimizing the BER for highly pathological channels (i.e. identifying the major contributors to signal degradation in the link). State-of-the-art pulse response analysis such as this, provides valuable insight into the behavior of the channel and the effective use of CTLE, FFE, and DFE equalization techniques, in order to mitigate crosstalk, attenuation and return loss.

Specific topics to be covered during this webcast include: optimization, BER, PAM-4, IBIS-AMI, S-parameters, causality, passivity, EQ, DFE, FFE, CTLE, and the latest in pulse response analysis and optimization.

Who should view this webcast:

Engineers and managers working on signal integrity design, characterization, and validation who want insight into the latest tips and techniques for optimizing the physical layer (package, PCBs & interconnects) for 32- to 56- Gbps communication links.