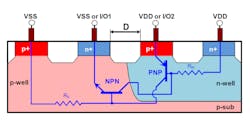

Latch-up susceptibility continues to be a growing concern for IC designers and verification engineers alike. Not only for Bulk designs, but also for FD-SOI which leverages hybrid bulk technologies for their IO devices. The good news is that context-aware latch-up verification can be automated to identify and validate the inadvertent structures and spacing requirements that make these checks so difficult to implement in traditional EDA tools.