Whitepaper: Accelerating Test Pattern Bring-Up for Rapid First Silicon Debug

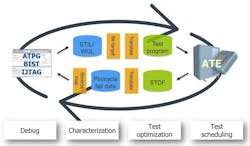

Reducing the time spent on silicon bring-up is critical in getting ICs into the hands of customers and staying competitive. Typically, the silicon bring-up process involves converting the test patterns to a tester-specific format and generating a test program that is executed by Automatic Test Equipment (ATE). This standard silicon bring-up flow is becoming too slow and expensive, especially for very large designs with complex DFT structures.