Tiny 24-Bit ADC Punches Through Multiple Performance Limitations

Engineering design requires balancing tradeoffs and limitations while dealing with real-world constraints, and deciding on the “best” balance for a given situation is a large part of the challenge. Components that minimize compromises among the specifications for multiple parameters simplify those decisions by enabling more degrees of freedom.

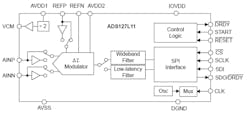

That’s where basic analog and mixed-signal building-block devices such as Texas Instruments’ ADS127L11 play a role (Fig. 1).

This single-channel, 24-bit, delta-sigma (ΔΣ) analog-to-digital converter (ADC) supports data rates up to 400 ksamples/s using the wideband filter and up to 1000 ksamples/s using the low-latency filter. The tiny 3- × 3-mm package—claimed to be 50% smaller than available alternatives—is just one of the many “breakthrough” attributes of this converter, which offers high performance for broad range of data-acquisition applications including medical, industrial, and grid-related projects.

Pushing Performance

The converter with SPI interface offers improved performance spanning a list of parameters. Power consumption is as low as 3.3 mW when sampling rates as high as 50 ksamples/s, a speed that’s compatible with many target applications. Designers can use wideband mode to improve ac measurement resolution with data rates as high as 400 ksamples/s, along with significantly wider bandwidth (50%), higher signal-to-noise ratio (30%), and lower latency (25%) than existing converters in this class, while minimizing noise at high frequencies.

In low-latency mode, the ADS12711 delivers 25% lower latency while sampling at up to 1000 ksamples/s. In addition, it lowers offset and gain drift by 89%—just 50 nV/°C and 0.6 ppm/°C, respectively—which improves dc measurement resolution, data throughput, and response times.

The device integrates input and reference buffers to reduce signal loading. Input signal range is nominally 0 to +5 V, while analog supply rails AVDD can be between 2.85 and 5.5 V (it’s actually somewhat more complicated; you’ll need to look at the datasheet for full details). The digital-side rail voltage can range between 1.65 and 5.5 V.

Multiple Converters

Although it’s “only” a one-channel device, many of the likely applications have a single- or low-channel count, so that’s not necessarily a limitation. For those situations needing more channels, the use of multiple ADS127L11 converters may still be an attractive option and yield high physical density due to the tiny size of the IC.

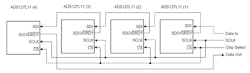

TI offers a nine-page application note “ADS127L11 in Simultaneous-Sampling Systems” that shows how to use a single clock and multiplexed ADS127L11 ICs for simultaneous, very low-skew multichannel sampling. It also details two arrangements for an SPI daisy chain offering serial, non-simultaneous sampling where channel-to-channel skew is less critical (Fig. 2).

The small size and focused functionality of this converter doesn’t imply correspondingly brief documentation. The comprehensive 90-page datasheet offers full details, performance graphs, and tabular specifications. There’s additional perspective on performance and tradeoffs in the associated blog posting “Balancing ADC size, power, resolution and bandwidth in precision data-acquisition systems.”

The complementary ADS127L11EVM-PDK Evaluation Module eases testing and understanding of this converter (Fig. 3). It includes hardware, software, and computer connectivity through a USB interface. The 35-page User's Guide features complete circuit descriptions, schematic diagrams, and a bill of materials.

The ADS127L11 ADC is specified for operation from −40 to 125°C. In addition to the 20-pin, 3- × 3-mm quad flat no-leads (WQFN) package, the ADS127L11 is available in a 6.5- × 4.4-mm thin-shrink small-outline (TSSOP) package. Pricing starts at $5.75 in 1,000-unit quantities.

References

“Balancing ADC size, power, resolution and bandwidth in precision data-acquisition systems”

About the Author

Bill Schweber

Contributing Editor

Bill Schweber is an electronics engineer who has written three textbooks on electronic communications systems, as well as hundreds of technical articles, opinion columns, and product features. In past roles, he worked as a technical website manager for multiple topic-specific sites for EE Times, as well as both the Executive Editor and Analog Editor at EDN.

At Analog Devices Inc., Bill was in marketing communications (public relations). As a result, he has been on both sides of the technical PR function, presenting company products, stories, and messages to the media and also as the recipient of these.

Prior to the MarCom role at Analog, Bill was associate editor of their respected technical journal and worked in their product marketing and applications engineering groups. Before those roles, he was at Instron Corp., doing hands-on analog- and power-circuit design and systems integration for materials-testing machine controls.

Bill has an MSEE (Univ. of Mass) and BSEE (Columbia Univ.), is a Registered Professional Engineer, and holds an Advanced Class amateur radio license. He has also planned, written, and presented online courses on a variety of engineering topics, including MOSFET basics, ADC selection, and driving LEDs.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: