Gallium-nitride (GaN) is becoming increasingly attractive in power electronics because the low switching losses of GaN enable high-frequency operation, which reduces the size of passive components without adversely impacting efficiency.

By employing a vertical FinFET GaN transistor design—for higher-voltage, higher-current switches, a vertical structure is preferred since its die area does not depend on the breakdown voltage—researchers from MIT, Cardiff, IQE (a Wales-based wafer and substrate maker), IBM, Columbia University, and the Singapore-MIT Alliance for Research and Technology have reported on development of a switch that handles voltages up to 1,200 V.

What’s more, the researchers report that with further work their FinFET device holds the promise of boosting capacity to the 3,300 V to 5,000 V range needed to bring the efficiencies of GaN to power electronics in the electrical grid itself.

Even at 1,200 V, the GaN device already has enough capacity to be considered alongside silicon-carbide (SiC) in addressing the power conversion needs of electric vehicles (EVs), but the researchers, who presented their paper at the IEEE International Electron Devices Meeting (San Francisco, Dec. 4-6), emphasize that they have thus far only produced a first prototype manufactured in an academic lab.

The leading GaN device architecture today is the High Electron Mobility Transistor (HeMT), which is a lateral device, meaning the entire device is fabricated on the top surface of the gallium-nitride wafer. While the resultant semiconductor is good for low-power applications like laptop chargers, the current and voltage demands for high-power conversion applications makes the chip area in a lateral topology so large that it becomes difficult to manufacture.

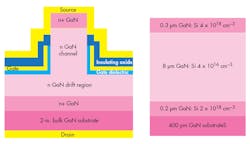

Schematic of the proposed GaN vertical fin power FET and its starting epi-structure. (Source MIT Technology Licensing Office)

Other drawbacks of lateral GaN FETs include (among other things): high leakage current; the larger dimensions and cost needed to yield higher voltage breakdown limits; non-uniform heat generation; the careful management of electric field profiles required in the lateral dimension between contacts (particularly in high voltage applications); the difficulties entailed in trying to make a normally-off device; reliability; maximum current limited by wire routing; and the lack of avalanche breakdown properties.

According to MIT professor of electrical engineering and computer science Tomás Palacios, senior author of the new paper, vertical devices are much better in terms of how much voltage they can manage and how much current they control. In these devices the current, instead of flowing through the surface of the semiconductor, flows through the wafer and across the semiconductor. This provides more space for input and output wires, enabling higher current loads, higher voltages, and higher efficiencies.

With lateral devices, on the other hand, all the current flows through a very narrow slab of material where the gate’s electric field can exert an influence on it; this area may be only 50nm in thickness and close to the surface. All the heat is being generated in this very narrow region and it gets extremely hot. In a vertical device, the current flows through the entire wafer, so heat dissipation is much more uniform.

In the past, researchers had attempted to build vertical transistors by embedding physical barriers in the gallium nitride to direct current into a channel beneath the gate. The barriers, however, were built from a costly material that’s difficult to produce, and integrating it with the surrounding gallium nitride in a way that doesn’t disrupt the transistor’s electronic properties proved challenging.

Rather than using an internal barrier to route current into a small region of a larger device, Palacios and his team used a narrower device. Their vertical gallium nitride transistors have bladelike protrusions known as “fins.” On both sides of each fin are electrical contacts that together act as a gate. Current enters the transistor through another contact, on top of the fin, and exits through the bottom of the device. The narrowness of the fin ensures that the gate electrode will be able to switch the transistor on and off.

Palacio attributes the clever idea of changing the geometry of the transistor—and thus confining the current geometrically by removing material from those regions where they don’t want the current to flow—to first authors Yuhao Zhang, a post-doctorate researcher in Palacios’ lab, and Min Sun, who received his MIT Ph.D. in the Department of Electrical Engineering and Computer Science (EECS). Other members of the team include Jie Hu, a postdoc in Palacios’s group; Zhihong Liu of the Singapore-MIT Alliance for Research and Technology; Xiang Gao of IQE; and Columbia’s Ken Shepard.

The fabricated transistor demonstrated a threshold voltage of 1 V and a specific on resistance of 0.36 mΩcm2. By proper electric field engineering, 800 V blocking voltage was achieved at a gate bias of 0V, the researchers reported.

About the Author

Murray Slovick

Contributing Editor

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: