DesignCon Mini Tour Highlights USB Type-C, Power, and Memory Test

If you’re heading to DesignCon next week, you should take a quick dip into Keysight’s booth to catch up on at least four topics of real import in high-speed design and test, and what to do about it.

I got a quick preview earlier this week: from USB Type-C and signal and power integrity, to PAM-4, 100G/400G data center standards and test and validation of the latest PCIe and DDR/LPDDR memory interface standards, it’s all there.

That said, I was disappointed in not seeing 5G wireless represented, but my virtual tour guides, Brad Doerr, R&D manager for Keysight’s Oscilloscope and Protocol Division, and Tami Pippert, Keysight’s high-speed digital marketing program manager, pointed to their 5G work being well represented in the conference papers, and will be brought into the booth for demos next year.

In the meantime, the booth will feature hands on demos aligned with some key product announcements and “with a focus on what we’re hearing from customers,” says Pippert, and top of mind is USB 3.1 Type-C.

“Type-C will drive [user]simplicity,” Pippert says, but the price will be some serious design and test complexity. Keysight will be showing solutions for compliance testing (which is still being defined by the USB Implementers Forum), as well as Tx/Rx Test Solutions and USB Type-C Alternate Mode Testing.

USB Type-C demos include the new the N8837A USB-PD Protocol Trigger and Decode and the N7015A Type-C test fixture that breaks out the connector into four channels.

Growing Need for Power Integrity

As devices become increasingly complex, operating at higher frequencies and lower voltages in smaller form factors, power integrity is coming up more and more with customers, according to Doerr. It’s not just about ensuring optimum power usage, but also making sure that, for example, sudden changes in the power rails don’t inject an error into the digital domain, causing a missed communication or an outright system failure.

It’s with that in mind that Keysight is showing its latest signal and power integrity solutions, the SIPro and PIPro EM analysis solutions for the ADS 2016, crosstalk analysis tools for oscilloscopes, and the latest PLTS 2016 (physical layer test system) software.

“Our new probes give a more accurate view of ripple, noise or coupling in a power system,” says Doerr. “It lets you capture it, zoom in, and correlate that to the rest of the system.”

With the N8833A crosstalk analysis package, for example, you can correlate crosstalk into a digital signal from the power system. What’s really cool is that you can graphically display the correlations between the victim and aggressor signal as you go from one power state to another.

The goal, said Doerr, is to really understand power distribution within a system at ultra-low (“microscopic”) power levels.

PAM-4 and 400GbE

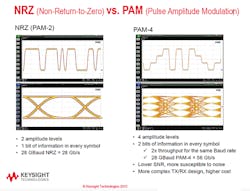

It’s would be hard to go through DesignCon and not bump into ChipHead, or someone else holding a PAM-4 eye diagram as they work feverishly to get to 100- and 400-Gbit/s Ethernet. Keysight is right there too, using the show to demo PAM-4 measurement application software for sampling and real-time oscilloscopes, as well as new system software for its M8000 series of bit error rate (BER) solutions. The software is required to control the J-BERT M8020A.

The move to PAM-4 for electrical signaling came quickly after it was decided by the IEEE P802.3bs in May of 2015 that it would use PAM-4 modulation for optical interfaces. Standardizng on an eight-lane interface for both electrical and optical greases the wheels to ecosystem mobility, while keeping costs down and technology and research advances on a common trajectory.

With 50 Gbits/s per channel, 400 GbE is attainable, but how soon, who’s closest, and at what cost Well, that’s why I’m going to DesignCon. See you next week!

About the Author

Patrick Mannion Blog

Founder and Managing Director

Patrick Mannion is Founder and Managing Director of ClariTek, LLC, a high-tech editorial services company. After graduating with a National Diploma in Electronic Engineering from the Dundalk Institute of Technology, he worked for three years in the industry before starting a career in b2b media and events. He has been covering the engineering, technology, design, and the electronics industry for 25 years. His various roles included Components and Communications Editor at Electronic Design and more recently Brand Director for UBM's Electronics media, including EDN, EETimes, Embedded.com, and TechOnline.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: