COVID-19 has turned a lot of people onto video streaming. However, it just accelerated an already growing trend. Streaming video is being used for all sorts of things, including live game streaming. Increased bandwidth and low latency are making video streaming very desirable, but bandwidth equals cost. To save money, bandwidth requirements can be reduced through transcoding.

Transcoding essentially converts data of some input format to an output format. Typically, this is done to compress video so that, say, a 4-Mb/s input stream scales down to 2.8 Mb/s. If the monthly cost of a gigabyte-per-second is $0.05, then 100K stream compressions will result in a cost savings of $21 million.

The Xilinx Real-Time (RT) Server reference design targets the video-streaming space (Fig. 1). The High Channel Density Video Appliance version contains up to eight Alveo U30 FPGA accelerator cards, while the Ultra-Low Bitrate Optimized Video Appliance integrates up to eight Alveo U50 cards.

The web-based interface allows for system management without dealing with the FPGA code. Xilinx integrated the Wowza Streaming Engine media server with the Xilinx RT Server Reference Architecture. The system uses the FFmpeg framework that’s compatible with other platforms that utilize CPUs or GPGPUs to handle transcoding chores. The HEVC codec was built from the ground up with emphasis on improved codec control down to the frame level. System integrators can adjust rate control and fine-tune other parameters to improve video quality and bitrate to suit their customer’s needs.

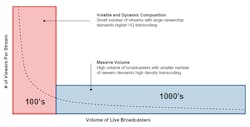

Supporting numerous different streams is important due to the rising level of live broadcasts (Fig. 2). Less transcoding is needed if a small number of streams will be watched by many people. At the other extreme is a large number of streams for a small group or an individual.

The delivery of an appliance is a big change for Xilinx that started with FPGA chips. These have become more integrated with SoCs like the Zynq, which combine CPUs with FPGA fabrics. The RFSOC family blends high-speed RF support into the mix. The adaptive compute acceleration platform (ACAP) even adds machine-learning acceleration.

It has recently moved into FPGA cards for the data center with the Alveo line, which is the basis for the Xilinx RT Server.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: