1.6-Tb/s Ethernet PHY Steps Up Security for Data Centers

A new family of secure 1.6-Tb/s Ethernet PHYs designed by Microchip Technology promises to keep up with the need for speed in enterprise switches, security appliances, and cloud service provider routers.

The networking chip vendor said the new META-DX2+ is the first Ethernet PHY to integrate 1.6 Tb/s of end-to-end encryption to secure data traveling through it. The new chip also features port aggregation so that the switches, routers, and other gear with it inside can use their port capacity more efficiently. All of these advanced networking abilities fit into the same compact footprint as its forerunner, the META-DX2L.

The amount of data traveling within data centers is on the rise, driven by the rollout of 5G networks and colossal data centers run by hyperscalers and cloud giants the likes of Amazon, Google, and Microsoft.

Microchip said that switches, routers, and other networking equipment targeted by the META-DX2+ Ethernet PHY need higher bandwidths, more port density, and flexibility to handle the deluge of data.

According to the company, META-DX2+, which belongs to the same family as the META-DX2L Ethernet PHY introduced last year, will double router and switch system capacity with up to 48 lanes of the latest 112G PAM4 SerDes for 800G ports.

The new devices can be configured as dual 800 GbE, quad 400 GbE, or 16x 100/50/25/10/1 GbE MAC/PHYs. They integrate 1.6-Tb/s hardware accelerators for MACsec and IPsec that can offload the packet processors in switches and other boxes of networking hardware.

Microchip said the META-DX2+ makes it simple to scale up to higher bandwidths with end-to-end encryption that runs in real-time—also called the "line-rate"—as data travels through enterprise switches, routers, or appliances with the PHY inside. Safeguarding critical data such as intellectual property (IP) or confidential records has long been a high priority when it comes to the cloud and enterprise data centers.

Port aggregation is another benefit afforded by the META-DX2+. Today, technology giants are upgrading to switches, routers, and other networking gear with 112G SerDes inside to support port rates up to 800G. But they are not upgrading everything at the same pace: Most ports in data centers run at less than 100G. A feature in the META-DX2+ family called ExpandIO funnels many of these ports into 112G SerDes lanes.

The Ethernet PHYs contain 32 or 48 112G PAM4 SerDes that can be programmed to improve speed or power savings, according to Microchip. The chips that come packed with 32 SerDes, including the META-DX2L, have compatible 23- × 30-mm packages. The chips that contain 48 SerDes share the same 33- × 33-mm package, enabling easy upgrades to new features (encryption, precision timing, and port aggregation).

Microchip is also courting telecom equipment makers with the new META-DX2+ series. The chips support the Class C/D Precision Time Protocol (PTP) to handle the very tight timing requirements of 5G networks.

The new Ethernet PHYs also have a highly configurable cross-point feature that gives them the flexibility to connect routing and switching silicon to a wide range of high-speed optics in a single device, improving the routing of components on the circuit board (PCB). They can transfer data over variable distances, including over backplanes and out through copper cables as well as into optical modules.

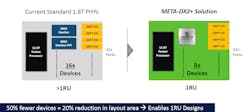

The chips have the flexibility to be used in “gearboxes” that convert a signal traveling over the sprawling networks inside data centers at one rate (for instance, 28G NRZ or 56G PAM4) and translate it to another (56G or 112G PAM4). Microchip said that while you would usually need a pair of Ethernet PHYs to supply 1.6 TB/s of performance, the META-DX2+ is a single-chip solution that saves more than 20% of space on the PCB.

With META-DX2+ and META-DX2L, “we now offer a complete chipset for all connectivity needs from retiming, gear-boxing, to advanced PHY functionality,” said Babak Samimi, head of Microchip's communications business.

All chips in the META-DX2 series leverage the same software development kit (SDK), which includes firmware and libraries in addition to support for the Open Compute Project (OCP) Switch Abstraction Interface (SAI) interface as well as networking operating systems (NOS) that support the SAI standard.

Samples of the new META-DX2+ Ethernet PHY line will be available in the fourth quarter.

About the Author

James Morra

Senior Editor

James Morra is the senior editor for Electronic Design, covering the semiconductor industry and new technology trends, with a focus on power electronics and power management. He also reports on the business behind electrical engineering, including the electronics supply chain. He joined Electronic Design in 2015 and is based in Chicago, Illinois.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: