Design for Test: ATPG keeps pace with design complexity

Automatic test-pattern generation (ATPG) has played a key role in semiconductor logic test, but several trends driving the need for semiconductor test quality are challenging traditional ATPG tools.

According to Robert Ruiz, senior marketing manager for test at Synopsys, 16-nm and 14-nm designs are increasingly adopting FinFET nodes. Chips are becoming increasingly complex, with designs having 5 million or more placed instances becoming common. The emergence of subtle defects is resulting in 50% of the defects not found with standard tests. And safety-critical automotive applications require less than one defect per million parts.

These trends, said Ruiz in a recent phone interview, are driving silicon test costs, impacting ATPG runtimes, and delaying the test of first silicon. Increasing compute cores per machine would seem to offer faster ATPG runtimes, but, said Ruiz, ATPG core usage is limited by memory, preventing full utilization of available cores.

To enhance ATPG performance to meet these challenges, Synopsys has introduced TetraMAX II ATPG, which boosts pattern-generation speed tenfold, cuts required patterns by 25%, and incorporates what Ruiz called production-proven interfaces for scan-rule checking and risk-free deployment.

In addition, SGS-TÜV Saar GmbH has certified TetraMAX II ATPG to ISO 26262 Automotive Safety Integrity Level (ASIL) D requirements for safety-critical automotive applications. “Tool qualification according to ISO 26262 is an important contribution to increased engineers’ confidence in the EDA software tools they use to develop automotive ICs targeted at electronic safety systems,” said Gudrun Neumann, product manager of Functional Safety Software at SGS-TÜV Saar, in a press release. “Satisfying the ISO 26262 for the most stringent ASIL D applications enables IC design teams to accelerate the overall functional safety certification requirements for their products. Synopsys’ TetraMAX II ATPG complies with the ASIL D safety requirements for software tools used in the development of safety-related electronic systems. SGS-TÜV Saar’s certificate for TetraMAX II is based on a successful functional safety evaluation of validation processes against the requirements of ISO 26262.”

Efficient fault targeting

Ruiz said TetraMAX II ATPG achieves benefits through more efficient multiple fault targeting. Traditional ATPG, he said, uses a sequential, slow method with little optimization to build a pattern by first targeting a primary fault, then a secondary fault, then a tertiary fault, and so on. In contrast, TetraMAX II ATPG employs what he called “iCubes,” each of which targets a fault. Many iCubes can be generated quickly in parallel across multiple cores, he said, and they can be intelligently combined to reduce the number of required patterns by 25%.

In addition, he said, TetraMAX II ATPG features fine-grain multithreading that eliminates the memory bottleneck, which speeds up pattern generation as cores are added, resulting in an order-of-magnitude runtime improvement.

Turnaround time can be reduced to a few days or hours for most complex designs, Ruiz said, allowing patterns to be available in time to test first-silicon samples. In addition, the 25% pattern reduction can be used to reduce time on the tester to lower test cost, or it can make room for additional high-quality slack-based or cell-aware patterns, he said. He noted that TetraMAX II ATPG generates the same pattern set regardless of the number of cores.

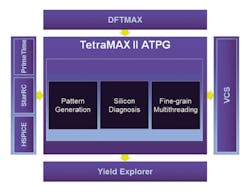

And finally, he said, TetraMAX II ATPG utilizes established links with Synopsys Galaxy Design Platform tools, such as the DFTMAX solution, the PrimeTime timing-analysis tool, and the StarRC extraction tool as well as other Synopsys tools including the Yield Explorer yield-management tool and Verdi debug tools (see figure).

Courtesy of Synopsys

Ruiz noted that customers including STMicroelectronics and Toshiba have seen faster pattern-generation runtime and reduced pattern sets using TetraMAX II ATPG. STMicroelectronics required fast turnaround time (TAT) for generating high-quality manufacturing test patterns, and Toshiba required a much faster ATPG solution that generates many fewer test patterns while being fully power-aware.

“Over the past several years, we have collaborated with Synopsys to address the growing manufacturing-test challenges of increasing complexity and manufacturing test costs in combination with requirements for higher quality and faster TAT,” said Roberto Mattiuzzo, SoC integration and DFT methodologies manager in STMicroelectronics’ Digital and Mixed Processes ASIC division, in a press release. “During our evaluation on a high-density FD-SOI chip, TetraMAX II produced test patterns an order of magnitude faster while significantly reducing the number of patterns without any coverage loss. With these results, we are confidently testing first-silicon samples earlier and reducing tester time, too.”

“Long ATPG runtimes and increasing test pattern counts are becoming bigger challenges on our large-scale SoC designs,” added Kazunari Horikawa, senior manager at Toshiba’s Design Technology Development Department. “Test pattern reduction within a short runtime is required to minimize test cost while maintaining the quality of test. We have been collaborating with Synopsys and confirmed through an evaluation that TetraMAX II shortens ATPG execution time and reduces the number of test patterns by up to 50% while maintaining the quality of test. We are planning to adopt TetraMAX II for our upcoming SoC designs and believe TetraMAX II will further reduce test cost with its strong roadmap.”

Toshiba shared its experience with TetraMAX II at the Synopsys Users Group India conference in Bangalore in July.

TetraMAX I and II are part of the Synopsys synthesis-based test solution, which also comprises DFTMAX Ultra and DFTMAX for power-aware logic test and physical diagnostics; DFTMAX LogicBIST for in-system self-test; SpyGlass DFT ADV for testability analysis; the DesignWare STAR Hierarchical System for hierarchical test of IP and cores on an SoC; the DesignWare STAR Memory System for embedded test, repair, and diagnostics; the Z01X fault simulator; Yield Explorer for design-centric yield analysis; and the Camelot software system for CAD navigation.

Hybrid approach combines ATPG and LBIST

For silicon test and yield analysis, Mentor Graphics offers its Tessent product suite, which includes, among other tools, Tessent FastScan for ATPG, Tessent LogicBIST for logic BIST (LBIST) insertion, and Tessent TestKompress, which employs compression techniques to minimize test data volume and reduce test time.

ATPG using a tool like Tessent FastScan has been the technique of choice for creating a set of deterministic test patterns for production test. ATPG requires an external tester to apply the patterns. In contrast, an LBIST tool like Tessent LogicBIST generates pseudorandom test patterns on chip and does not require an external tester. Consequently, LBIST can be used for field test or in burn-in and test applications.

“One unique value of LBIST is that the test can be autonomous—initiated and verified in any test environment, even if an external tester is not available,” writes Ron Press, technical marketing director for silicon test solutions products at Mentor Graphics, in a blog post.1 “ATPG, on the other hand, requires the use of an external tester but provides a very high precision of pattern application.” Specialized fault targeting for timing-aware, cell-aware, path-delay, bridge, and other fault models increases the number of required patterns, in turn necessitating the use of embedded compression, he adds.

Increasingly, engineers want to apply both ATPG and LBIST, especially for safety-critical applications. The downside, writes Press, is that LBIST’s linear feedback shift register (LFSR) and ATPG’s decompressor, multiple-input signature register (MISR), and compression compactor use different logic, requiring more silicon area for test logic.

Mentor’s approach to this problem is embodied in its Tessent Hybrid TK/LBIST technology, in which LBIST and the compression required for embedded deterministic test2 share a majority of the decompressor/LFSR and compactor/MISR logic.

Concludes Press, “The Tessent Hybrid solution … enables designers to reap the benefits of both ATPG compression and LBIST, delivering significant efficiency improvements and addressing the requirements for in-system test required for safety-critical applications.”

References

- Press, R., “Getting the best of ATPG and LBIST—a Hybrid Test Solution for Autonomous &

High-precision IC Test,” Silicon Test and Yield Analysis Blog, Mentor Graphics, July 14, 2016. - Neerkundar, V., “Using EDT Test Points to reduce test time and cost,” EE-Evaluation Engineering, November 2015, p. 36.

About the Author

Rick Nelson

Contributing Editor

Rick is currently Contributing Technical Editor. He was Executive Editor for EE in 2011-2018. Previously he served on several publications, including EDN and Vision Systems Design, and has received awards for signed editorials from the American Society of Business Publication Editors. He began as a design engineer at General Electric and Litton Industries and earned a BSEE degree from Penn State.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: