The Transistor Enters the Nanosheet Era

This article is part of Electronic Design’s 2024 Technology Forecast series. It's also part of the TechXchange: Distinguishing Discretes.

What you'll learn:

- How does a nanosheet transistor compare with a FinFET?

- Issues involved in developing and manufacturing nanosheet transistors.

- Benefits of adopting nanosheet transistors in chip design.

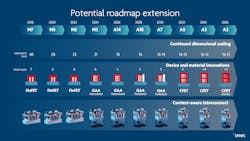

It’s the end of the transistor as we know it. The world’s most advanced chip companies are racing to roll out a new generation of transistors based on the gate-all-around (GAA) architecture at scale. While they’re all at varying stages of the transition, they intend to start integrating these “nanosheet” transistors at 3- and 2-nm process nodes, with mass production likely hitting its stride in 2024 and into 2025.

It will take time for the likes of Intel and TSMC to unlock the full potential of these transistors and the larger semiconductor industry to feel the full impact of the transition. But such devices are bound to become the gold standard in CPUs, GPUs, and other advanced logic chips at the heart of everything from AI to high-performance computing (HPC). These transistors are designed to be faster and less power-hungry, defying the limitations of the FinFET that has long dominated the semiconductor arena.

Nanosheet transistors aren’t about to save Moore’s Law, nor can they solve all of the challenges faced by foundries at state-of-the-art process nodes. To overcome those, foundries are pursuing a wide range of innovations such as backside power delivery (BSPD) to wring more performance out of the interconnects between transistors while saving power.

They’re also adopting new approaches to chip design, namely system technology co-optimization (STCO). STCO involves linking chiplets with 2.5D and 3D advanced packaging.

While the nanosheet has its limits, the semiconductor industry is giving its all to the transition. For its part, Intel intends to introduce the RibbonFET—its unique formulation of the nanosheet—in upcoming process nodes. It will start with the “20A” node, which the company said is on tap for the first half of 2024. TSMC plans to adopt the nanosheet for the first time in its 2-nm node hitting the market by early 2025.

While more of a secondary player in the market for logic chips, Samsung rolled out a variation of the nanosheet—called the Multi-Bridge-Channel FET (MBCFET)—before anyone else with its 3-nm node in 2022.

To better understand the case in favor of the nanosheet and its unique advantages, we consulted Julien Ryckaert, VP of logic technologies at imec, one of the world’s leading semiconductor research labs.

This interview has been condensed and edited for clarity.

To set the stage for the nanosheet, what was the argument in favor of the FinFET in the first place?

The nanosheet transistor is really a continuation of the FinFET. The main reason that everyone started investigating these kinds of 3D architectures was short channel control.

It was becoming harder and harder as you scaled the gate length of planar transistors to maintain the isolation between the source and the drain and to make sure that you have sufficient cutoff whenever you turn off the transistor. We want to limit these what we call “short channel effects,” and the ability to do that is usually characterized by a metric we call “subthreshold slope.”

You ensure a proper cutoff by making sure that the whole channel is cut off during the off state. So, as the gate length scales down, the drain gets physically closer and closer to the source, right? And then it starts to become more difficult to guarantee the isolation between the two terminals.

So, you start looking at ways to confine the channel so that whenever you turn off the transistor, the field is strong enough inside the semiconductor region to guarantee that the drain and source remain isolated.

Everyone converged on this fin-shaped device, which is a slice of silicon standing out [from the silicon wafer] where the gate would wrap around the structure and guarantee a well-controlled off-state and, thus, ensure subthreshold slope as you scale the gate.

Are there any other forces at work that pushed the semiconductor industry to adopt the FinFET?

I’m not sure it was part of the thought process when the FinFET was being developed. But a large portion of the width (W) of the channel [a characteristic closely related to the amount of current that it takes to switch the transistor off and on] is in the vertical direction, the height of the fin. The taller the fin, the more W you create for the FinFET, the more drive current you create for the transistor.

This was very useful in the scaling of the FinFET because you could now create a transistor that was very compact with sufficient drive current. Chipmakers exploited this extensively in the FinFET generations, depopulating the number of fins in the transistor and compensating for that by increasing the height of the fins. If you want to scale the W in a planar transistor, it will have to occupy more and more space.

So, the standard cells, which are the building blocks of logic libraries, ended up moving from a three-fin device to a dual-fin device. The knob that companies turned to scale the transistors was called “track height scaling.” You could scale the standard cell structurally without scaling the pitches, simply because you could depopulate the number of fins and, instead, use taller and taller fins. So, there are two arguments in favor of the FinFET—one is better electrostatic control, the other is better efficiency.

Then, tell me why the semiconductor industry is trying to replace the FinFET, despite all its advantages. Why is it at the end of its rope?

Let me preface this by saying that although the transition from planar- to fin-shaped transistors was a no-brainer, the nanosheet will unfortunately have a harder time bringing the same benefits that we’ve seen from the FinFET.

The reason we’re moving to nanosheet is mostly because of electrostatic control. You previously used a fin that was anchored into the wafer, and it required the fin to have a very straight profile, so you needed a thin fin of very straight silicon from the top to the bottom—the foot of the fin—to make sure that you have precise control across the channel.

However, the fin profiles are never perfectly straight, so you always have some degree of power leaking from the bottom of the fin. Some of the major foundries are trying to improve the fin profile to guarantee the electrostatic control. But honestly, there’s only so much you can do.

At the same time, everyone wanted to scale the gate length of the transistor, but they realized that it was getting more challenging to keep scaling the fin and the gate length at the same time and still guarantee the same electrostatic control.

What’s happening is we’re moving to a complete GAA structure, where the whole channel is wrapped around on all four sides to get the strong gate field that can guarantee a strong turn on and turn off and reduce leakage current. That way, you can continue to scale the gate length within the nanosheet device.

So, is it simply no longer sustainable to use the FinFET at the scale of the most advanced process nodes? What is the payoff for companies that can figure out nanosheet technology?

Right. The problem is just a matter of geometry. As you manufacture smaller and smaller transistors, you end up with a pair of fins per device. The next step is to explore the possibility of a single-fin device, right? But the problem with a single fin, if you want to maintain the drive current that you had with a pair of fins, is you need to double the height of the single fin.

So, for instance, maybe the fin is 50-nm high in a double-fin scenario. With a single fin, you would have to go to a 100-nm fin, which is very tall and, as a result, very tough to manufacture in a cost-efficient way.

And at the same time, the amount of parasitics [most notably the capacitance and resistance] that you accumulate in such a tall structure would deplete all the advantages of making the device more compact in the first place. So, it’s not as though the 100-nm fin would work as well as a pair of 50-nm fins placed side-by-side.

When we realized that the two-fin device was close to the end of its life, it turned out geometrically chopping the single fin into slabs—for example, 20 to 25 nm tall—and then stacking them on top of each other with the gate wrapping around [the channel] gives you the best compromise in terms of effective width [maximizing drive current] and minimizing parasitics [in the same footprint that would fit a single fin]. It’s just pure geometry.

This is why companies have started investing in the transition to nanosheet transistors, and it is also why you see different foundries taking different trajectories. Some foundries have introduced nanosheet before others, and that is simply because the nanosheet and the FinFET are still competing for dominance at these dimensions—in terms of striking [a balance between] the efficiency, drive, and parasitics of the device.

You’re saying that they are all trying to determine when it is worth it to go through the trouble of transitioning to the nanosheet.

Exactly. We know the separation between the two fins is limited by how much metal you can squeeze between the two fins to form the gate, so at some point you will get stuck with one single fin, and with a single fin, you know you’re toast. You can’t get the same power and performance improvements without the nanosheet. The crossover point depends on your trajectory, but that happens at around 3-nm or 2-nm node dimensions.

If you’re a leading foundry and you’ve mastered the fabrication of fins, you’ll try to squeeze the most you can out of the FinFET. But it all depends on your manufacturing capabilities, what you consider the leading edge, and how fast you want to get to market. Some companies are trying to capitalize on the nanosheet revolution as soon as possible.

The argument in terms of power and performance, I would say it is virtually equal to the FinFET. But you know you will have to [shift] to the nanosheet at some point because the FinFET no longer scales, no longer gives you more transistors per unit area.

So, the semiconductor industry stopped a long time ago naming process nodes based on any specific measurement in the transistors. Instead, it’s mostly a way of highlighting how advanced a process node is.

Given that, are companies scaling the transistors at all with nanosheet technology? It seems to be more about improving the transistor’s performance compared to the FinFET rather than reducing its footprint. The area savings seem more secondary with the nanosheet.

It’s the latter. Another way to look at it is, imagine that scaling is forcing you shrink the area of a standard cell. You are trying to squeeze the two types of transistors—the n-channel (nFETs) and p-channel FETs (pFETs)—used to create CMOS logic. They all need to fit within the footprint of a standard cell, so you start breaking the problem down into all the rules you must obey. How far apart can the fins be? How far can the FETs be from each other? How much gate length do you need to provide to get everything under control?

You analyze all these constraints on transistor placement, and then you realize it’s impossible to fit two fins into the device anymore in the footprint you’re giving yourself at that specific node. You cannot get a pair of nFET and pFET transistors in the same space anymore, you can only get one fin on the nFET and one fin on the pFET. Then, parasitics dominate. And the fin is so tall that it’s impossible to manufacture.

These slab-shaped transistors allow you to better use the footprint available to you [to create a larger effective channel width compared to the FinFET] and to squeeze the transistors together in a way that [increases the device drive current capability]. Since the structure stays shallow or at least as tall as it used to be before, you are not accumulating too many parasitics.

So, when comparing the power, performance, area of a FinFET to a nanosheet transistor at the same dimensions, you will see the FinFET starts tanking in performance at about the 2-nm node. The nanosheet can continue to maintain the performance, power, and area gains that companies mostly want today. But you’re not going to see sudden massive gains coming out of the nanosheet. However, it ultimately depends on how fast some of these foundries are going to start turning all these knobs.

Companies around the chip industry are getting everything from the manufacturing tools to EDA software that can capture all intricacies of the nanosheet FET. What else comes to mind when you think about what needs to fall into place for chips based on nanosheet transistors to hit the market?

First off, as far as I know, it will be very challenging to provide I/Os, so the large set of devices that a standard CMOS platform offers. There are many difficulties in co-integrating other types of devices with the nanosheet. That means a lot of new intellectual property (IP) will have to be designed to guarantee a proper SoC subsystem. The I/Os will not be available.

And while it may not be directly related to the nanosheet, remember that the transition to the nanosheet coincides with a number of changes in how semiconductor companies will have to do design. The other transition that some companies plan to go through at the 2-nm node is backside power delivery.

No matter how you look at it, there are lots of changes converging at the same time—both for the foundries and fabless companies. You’ve got to have strong shoulders to get into these transitions.

Are there other unique advantages to the nanosheet besides improvements to transistor density?

There are some opportunities that are unique to the nanosheet that the design community will be able to exploit. One of these opportunities—and we have studied this extensively with Cadence—is the fact that, even though it is a stacked structure, the width of the device is not [set in stone] anymore, which is the way it was with fins.

With the FinFET, it was four fins, three fins, or two fins, right? However, with the nanosheet, you could envision a modulation of the sheet width almost in a continuous fashion.

Now, it’s very difficult to put that into a manufacturing process, which is why you probably will not see the opportunity offered in the first generations of nanosheet. But the ability to modulate the sheet width from 25 to 20 to 15 to 10 nm will give you another knob for optimizing the power and performance of the SoC [since adjusting the channel width affects the parasitic capacitance of the transistor]. So, if foundries can figure out the technology, fabless companies will be able to access a better power-versus-performance tradeoff.

There will need to be little changes to the process flow to make modulation possible, which is why it will take some time to become available. But it is potentially a very, very powerful knob that you can activate.

As the FinFET runs out of road, the chip industry is starting to shift its focus to other innovations, most notably chiplets and advanced packaging. I’m sort of wondering, in that context, do you think that the nanosheet transistor will make the same sort of impact as the FinFET? Or are we entering a phase where it’s just another tool in the toolbox?

I think it’s just another tool in an ever-widening toolbox. I think the world where the transistor dominates the whole semiconductor roadmap is kind of over with now.

It’s important to keep density scaling with new devices, and getting more compact transistors will remain a key factor in scaling. But I think foundries will have to complement it with more offerings—so, innovation in the middle and the backend of the manufacturing process [where the interconnects and contacts on the device are shaped].

A key factor in the device’s real estate and even its performance is not even determined by its channel and other properties of the transistor itself. But it’s equally determined by how you access the device, right? And the three major foundries have drastically different middle-of-the-line (MOL) strategies, which is a sign that it’s a place where it may still be possible to innovate and introduce new solutions.

In the future, 3D chip-stacking and chiplet-like approaches may also become more important to complement the transistor’s roadmap. One of the key issues with the nanosheet transition is that SRAM will not scale or hardly scale in terms of density compared to the FinFET. So, if half of the processor is composed of SRAM, you can assume that half of the product will not scale. That’s not only unfortunate, but it will also force chip designers to find other solutions to solve that bottleneck.

Read more articles in Electronic Design’s 2024 Technology Forecast series, and in the TechXchange: Distinguishing Discretes.

About the Author

James Morra

Senior Editor

James Morra is the senior editor for Electronic Design, covering the semiconductor industry and new technology trends, with a focus on power electronics and power management. He also reports on the business behind electrical engineering, including the electronics supply chain. He joined Electronic Design in 2015 and is based in Chicago, Illinois.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: