SoC Incorporates Hardware Scheduling and EtherCAT Support

Most new microcontrollers offer faster clock speeds, more memory, and sometimes some interesting peripherals. Price, power efficiency, and size tend to control the buying requirements in choosing a micro for an application. But occasionally a micro stands out because of one or more new features.

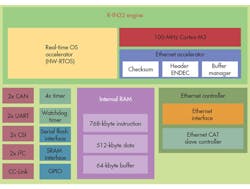

Based on ARM’s Cortex-M3 microcontroller, Renesas’ R-IN32M3 boasts hardware enhancements that reduce system overhead and, hence, power utilization. It also provides more headroom for user applications (Fig. 1). It will have a major impact on industrial automation by providing a very efficient, low-cost platform.

OS Hardware Acceleration

The R-IN32M3 is not the first platform to incorporate operating-system (OS) acceleration hardware or hardware-based scheduling, but the implementation level is very uncommon in this class of microcontrollers. The HW-RTOS block’s more sophisticated interrupt service manager knows about task control blocks, semaphores, event flags, and mailboxes, which are implemented in hardware and tied to a hardware scheduler.

This works with the standard ARM nested vectored interrupt controller (NVIC). The big difference is that the hardware does much of the work typically performed in software to handle interrupts and task switching. This is faster, and many operations can be completed in parallel. Likewise, hardware alone can handle some operations, such as an interrupt setting a semaphore or deciding what task will be run next.

Micrium has customized a version of its µC/OS III to take advantage of the R-IN32M3. The main difference a programmer will see between a stock version and the enhanced version is that the tasks and priorities are more limited. Software tends to be limited by memory, while hardware is limited by what is implemented in hardware.

For example, the R-IN32M3 version of µC/OS III is limited to 64 tasks with 16 priorities. The limit on semaphores is 128, and there may only be 64 message queues. These limits would be a concern for some µC/OS III platforms that are faster and have more memory, but they should be sufficient for most applications running on a Cortex-M3.

Slaving Over EtherCAT

The R-IN32M3’s dual Ethernet ports are designed to handle EtherCAT in hardware. Heavily used in industrial automation, EtherCAT always forms a logical ring and timestamps each packet (see “Industrial Automation Relies On Ethernet” on electronicdesign.com). The device also needs to process packets as they pass around the ring, so the amount of software overhead can be high unless there is hardware acceleration like that provided by the R-IN32M3. There are two Ethernet ports because EtherCAT slaves are designed for daisy-chain configurations that are popular in industrial control. They also can provide redundancy if the physical loop is closed.

The Renesas R-IN32M3-EC development board is available as an IAR KickStart package (Fig. 2). The R-IN32M3 chip is available in two vesions. The R-IN32M3-EC has 10/100 ports with built-in PHYs with the EtherCAT slave controller. The R-IN32M3-CL supports Gigabit Ethernet and uses external PHYs and has the CC-Link IE Field slave controller.

About the Author

William Wong Blog

Senior Content Director

Bill's latest articles are listed on this author page, William G. Wong.

The latest blogs have been moved to alt.embedded on Electronic Design.

Bill Wong covers Digital, Embedded, Systems and Software topics at Electronic Design. He writes a number of columns, including Lab Bench and alt.embedded, plus Bill's Workbench hands-on column. Bill is a Georgia Tech alumni with a B.S in Electrical Engineering and a master's degree in computer science for Rutgers, The State University of New Jersey.

He has written a dozen books and was the first Director of PC Labs at PC Magazine. He has worked in the computer and publication industry for almost 40 years and has been with Electronic Design since 2000. He helps run the Mercer Science and Engineering Fair in Mercer County, NJ.

- Check out more articles by Bill Wong on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: