Post-Quantum Crypto Secures FPGA Boot

What you’ll learn:

- What is post-quantum cryptography?

- Why post-quantum cryptography secure boot is important.

- What new features have been built into the Agilex 5 D-Series FPGAs?

Altera has finally spun off from Intel, allowing Altera to focus on FPGA chips and tools. Its latest release is the Agilex 5 D-Series that fits in the middle of its FPGA portfolio (Fig. 1). The Agilex FPGAs can also incorporate hard Arm CPU logic like the dual-core Arm Cortex-A55 plus dual-core Arm Cortex-A76 hard logic. The Agilex 9 family supports Direct RF technology.

Using Post-Quantum Cryptographic Secure Boot

The Agilex portfolio consists of RAM-based FPGAs, in which the configuration is contained in serial memory that’s read into RAM at boot time (Fig. 2). Secure boot has been a feature, but it utilized pre-quantum cryptography algorithms. This was fine until quantum computing started to move toward practical implementations.

While quantum computing isn’t mainstream, it’s moving in that direction. Once adopted, it will make breaking most pre-quantum cryptography algorithms trivial, which is spelled out in the video on NIST-adopted new post-quantum cryptography algorithms last year.

The Agilex 5 D-Series provides post-quantum cryptography (PCQ) secure boot in addition to performance and capacity improvements. The feature is essentially transparent to developers, as was the pre-quantum incarnations. Developers only need to be concerned with creating the boot configuration. The hardware handles the boot process and its matching crypto support.

Higher Performance and Capacity of the Agilex 5 D-Series

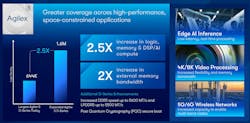

PCQ secure boot is a significant new feature of Agilex 5 D-Series, but it’s far from the only new aspect. It bumps up the number of logic table units (LTUs) at the top end from 644K to 1.6M LUTs. The internal memory bandwidth has been doubled and the 2.5X improvement in logic extends to the DSP and artificial-intelligence (AI) support as well as internal memory.

The external DDR5 memory interface was also bumped up to 5,600 Mtransfers/s while LPDDR5 speeds were increase to 5,500 Mtransfers/s. The FPGAs support 4K/8K video processing as well.

FPGA Development Tools Streamline Design Processes

Altera announced updates to its design tools, including Quartus Prime (Fig. 3). This FPGA design tool supports the entire Agilex portfolio. Improvements were made to the compiler, which runs 27% faster than its predecessor. It also optimizes designs employing Altera’s Adaptive Logic Module (ALM), initially introduced in the earlier Stratix FPGA family.

A key component of Quartus Prime is Visual Design Studio (Fig. 4). It employs a drag-and-drop design process with enhanced productivity features to cut creation time from days to hours. Designers can use it to combine IP quickly. Projects that would take days can often be completed in hours utilizing Visual Design Studio.

>>Check out this TechXchange for similar articles and videos

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: