Real-Time MCU First to Integrate NPU

The TMS320F28P550SJ from Texas Instruments is the industry's first real-time MCU with an integrated neural processing unit (NPU). It's designed to run convolutional-neural-network (CNN) models to help reduce latency and power usage when monitoring and detecting for arc or motor faults.

The device is capable of functional-safety applications with documentation available to aid ISO 26262 and IEC 61508 system design/systematic capability up to ASIL D. Also targeted are SIL 3 and hardware integrity up to ASIL B.

The NPU in the TMS320F28P55x series offloads the execution of the neural-network model from the main CPU, achieving 5X to 10X lower latency than software implementations to enable faster, more accurate decision-making. Further, the model that runs on the integrated NPU learns and adapts to different environments through training, helping systems achieve greater than 99% fault detection accuracy to enable more informed decision-making at the edge.

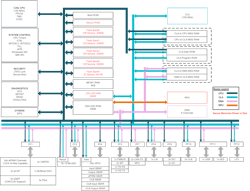

This device is supported by Edge AI Studio, a collection of tools to help engineers with any level of experience easily complete the AI model development process. A functional block diagram (see figure) shows the rich number of resources available for applications in automotive, industrial, consumer, telecom, server, and building automation, among many others.

The Core

The real-time control subsystem is based on TI’s 32-bit C28x DSP core, which provides 150 MHz of signal-processing performance for floating-point or fixed-point code running from either on-chip flash or SRAM. TI claims processing equivalency to a 300-MHz Arm Cortex-M7-based device on a real-time signal chain.

The device features an IEEE 754 single-precision floating-point unit (FPU32) and a trigonometric math unit (TMU). It provides support for nonlinear proportional integral derivative (NLPID) control and integrates a CRC Engine and Instructions (VCRC), speeding up common algorithms key to real-time control systems.

On-chip memory includes:

- 1,088 kB of flash (ECC-protected) across five

independent banks:- Four 256-kB banks

- One 64-kB bank, ideal for LFU/Bootloaders/

data

- 8 kB of OTP (one-time-programmable flash

memory) - 133 kB of RAM (ECC/parity protected)

Peripherals and I/O

System peripherals include a six-channel direct-memory-access (DMA) controller, 91 individually programmable multiplexed general-purpose input/output (GPIO) pins (22 shared with Analog) and 17 digital inputs on analog pins

The 3.3-V I/O design incorporates internal regulators to facilitate single-supply operation. Included is 5-V fail-safe and tolerant capability on four GPIOs for PMBus/I2C support and configurable 1.35-V VIH on four GPIOs for interfacing to nanometer-scale devices.

Communication peripherals include a Power-Management Bus (PMBus) interface, two inter-integrated circuit (I2C) interfaces, two Controller Area Network with Flexible Data-Rate (CAN FD/MCAN) bus ports, one Universal Serial Bus (USB 2.0 MAC + PHY), two Serial Peripheral Interface (SPI) ports, three UART-compatible Serial Communication Interfaces (SCI), one UART-compatible local interconnect network (LIN) interface, and a Fast Serial Interface (FSI) with one transmitter and one receiver (up to 200 Mb/s).

Analog Resources

The device's analog system includes five 3.9 MSPS, 12-bit analog-to-digital converters (ADCs), up to 39 external channels (includes one gpdac output), four integrated post-processing blocks (PPBs) per ADC, four windowed comparators (CMPSS) with 12-bit reference digital-to-analog converters (DACs) that feature digital glitch filters and low DAC output to pin capability on CMPSS1.

The analog system also includes one 12-bit buffered DAC output and three programmable gain amplifiers (PGAs) that feature unity gain support, inverting and non-inverting gain mode support, and programmable output filtering.

Enhanced Pulse Capability and...CLBs

Enhanced Control peripherals include 24 ePWM channels with 12 channels that have high-resolution capability (150-ps resolution), two Enhanced Capture (eCAP) modules, three Enhanced Quadrature Encoder Pulse (eQEP) modules with support for CW/CCW operation modes, and an embedded pattern generator (EPG).

TI's Swiss Army knife also includes two tiles of configurable logic blocks (CLBs) that augment existing peripheral capability and support position manager solutions.

NPU

The NPU is capable of 600 MOPS (megaoperations per second) at 75 MHz on 8bWx8bD (W=weight, D=data) and 1,200 MOPS at 7 5MHz on 4bWx8bD, and it can support machine-learning inferencing using pre-trained models. The NPU is highly optimized for deep convolutional neural networks (CNNs) and has up to 10X neural-network inferencing performance improvement vs. SW techniques.

TI claims that no direct coding is required because TI AI tools generate FW libraries that include real-time-control, focused edge AI models with example applications that include arc-fault and motor-fault detection.

"TI designed the TMS320F28P550SJ MCU to transform the way we monitor for faults," said Vinay Agrawal, product line manager, Industrial Application Specific Microcontrollers, at Texas Instruments. "Think of applications like arc fault detection in solar and energy storage systems, motor-bearing fault detection for predictive maintenance in industrial machinery, and fan blade imbalance faults in HVACs. Traditional monitoring methods, such as rules-based detection, require a lot of system expertise and are often limited in their adaptivity, sensitivity and accuracy.

"In comparison, the integrated AI hardware accelerator in our MCU helps increase overall system efficiency and safety by running neural-network models in real-time. These models can be trained with raw or preprocessed sensor data such as motor vibration signals, solar DC currents, or battery voltage and current, enhancing detection of subtle variations that indicate faults. By more accurately identifying faults or predicting failures, designers can significantly enhance system reliability while preventing costly downtime and improving overall performance."

The device series is available at TI for about $4 in 1k quantities , depending on part number and package.

A variety of hardware evaluation boards are also available. One example is the LAUNCHXL-F28P55X, a low-cost ($29 from TI) development board for TI C2000 real-time microcontrollers series of F28P55x devices.

For Electronic Design readers' convenience, the TMS320F28P55x Real-Time Microcontrollers datasheet is provided below, though it would be wise to obtain the latest revision and other TMS320F28P55x design resources from TI before starting a design.

To keep up with Electronic Design’s latest automotive-related articles, please subscribe to our Automotive Electronics bi-weekly newsletter.

Glossary

AI model development: Process of creating machine-learning models using tools like edge AI Studio, which automates tasks like data preprocessing, training, and deployment.

Analog-to-digital converter (ADC): 12-bit, 3.9-MSPS converter that transforms analog signals (e.g., sensor data) into digital values for processing. The device includes five ADCs with up to 39 external channels.

ASIL (Automotive Safety Integrity Level): Risk classification system (A-D) defined by ISO 26262 for functional safety in vehicles. The MCU targets ASIL D systematic capability and ASIL B hardware integrity.

CAN FD/MCAN: Controller Area Network with Flexible Data-Rate, enabling high-speed communication (up to 8 Mb/s) for automotive/industrial networks.

C28x DSP core: 32-bit Texas Instruments DSP optimized for real-time control, delivering 150-MHz performance with floating-point (FPU32) and trigonometric math units (TMUs).

Configurable logic block (CLB): Two programmable logic tiles that extend peripheral functionality, enabling custom digital logic without external components.

Convolutional neural network (CNN): AI architecture specialized for image/pattern recognition, optimized here by the NPU for fault-detection tasks.

CRC Engine: Hardware accelerator for Cyclic Redundancy Check calculations, ensuring data integrity in communication protocols.

Edge AI Studio: TI's toolset simplifying AI model deployment on embedded devices, including pre-trained models for fault detection.

ECC (error-correction code): Memory protection mechanism detecting/correcting bit errors in flash (1088 kB) and RAM (133 kB).

ePWM (enhanced pulse-width modulator): 24-channel peripheral for precise motor control, with 12 high-resolution (150 ps) channels.

FSI (Fast Serial Interface): 200-Mb/s communication interface for high-speed data transfer between components.

Functional safety: System design approach (ISO 26262/IEC 61508) ensuring fail-safe operation in automotive/industrial applications.

IEC 61508: International standard for electrical/electronic/programmable safety-related systems, with Safety Integrity Levels (SIL 1-4).

Neural processing unit (NPU): Dedicated AI accelerator achieving 600 to 1,200 MOPS for CNN inference, enabling 99% fault-detection accuracy with 10X lower latency than software.

Nonlinear PID control: Advanced control algorithm supported by hardware accelerators for managing complex systems like motors.

OTP (one-time programmable): 8-kB secure memory for storing encryption keys or calibration data.

PMBus: Power Management Bus standard for digital communication with power supplies.

SIL 3: Safety Integrity Level 3 under IEC 61508, indicating <0.001 probability of dangerous failure per hour.

VCRC (vertical redundancy check): Instruction-level CRC acceleration for real-time data validation.9

***

This glossary was autogenerated and hand-checked.

About the Author

Andy Turudic

Technology Editor, Electronic Design

Andy Turudic is a Technology Editor for Electronic Design Magazine, primarily covering Analog and Mixed-Signal circuits and devices and also is Editor of ED's bi-weekly Automotive Electronics newsletter.

He holds a Bachelor's in EE from the University of Windsor (Ontario Canada) and has been involved in electronics, semiconductors, and gearhead stuff, for a bit over a half century. Andy also enjoys teaching his engineerlings at Portland Community College as a part-time professor in their EET program.

"AndyT" brings his multidisciplinary engineering experience from companies that include National Semiconductor (now Texas Instruments), Altera (Intel), Agere, Zarlink, TriQuint,(now Qorvo), SW Bell (managing a research team at Bellcore, Bell Labs and Rockwell Science Center), Bell-Northern Research, and Northern Telecom.

After hours, when he's not working on the latest invention to add to his portfolio of 16 issued US patents, or on his DARPA Challenge drone entry, he's lending advice and experience to the electric vehicle conversion community from his mountain lair in the Pacific Northwet[sic].

AndyT's engineering blog, "Nonlinearities," publishes the 1st and 3rd Tuesday of each month. Andy's OpEd may appear at other times, with fair warning given by the Vu meter pic. His cartoon series, "Inventors", appears each week in Electronic Design Weekly.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: