MoSys’ Graph Memory Engine Accelerator IP Targets Packet Classification on Intel’s Stratix 10 FPGAs

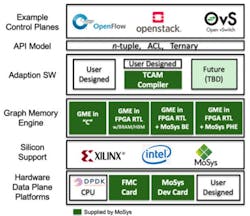

MoSys announced that its Graph Memory Engine (GME) Accelerator IP is now running on Intel Stratix 10 FPGAs. The GME is part of MoSys’ Packet Classification Platform, and is capable of performing embedded search and classification of packet headers. The proprietary platform software enables the compilation of TCAM images into graphs for GME processing. The GME product offering includes software, firmware and RTL and utilizes a common API and common RTL interface to facilitate platform portability.

Three implementations of GME will be available, including pure hardware-agnostic, software version offering maximum flexibility and capacity, and an RTL-only version for use in an Intel FPGA for hardware-accelerated performance with no external MoSys memory device required. As it is RTL only, in addition to new designs, installed -legacy systems can be reprogrammed to provide increased performance.

Packet classification applications can now run faster because the search performance on an FPGA when combined with a MoSys PHE can result in up to 100x performance improvement over a software solution running on a single core of CPU with DRAM. An implementation that utilizes the MoSys PHE provides enough additional performance to support the search throughput needed for two 100G ethernet ports.

For more information visit www.mosys.com