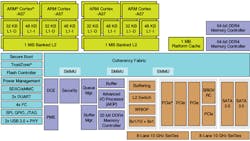

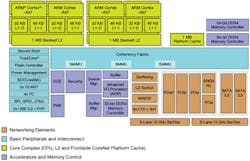

Freescale’s latest crop of QorIQ LS2 system-on-chip (SoC) solutions are based on Arm’s Cortex-A50 ARM-8 architecture (see “Delivering 64-Bit Arm Platforms” on electronicdesign.com) and Freescale’s Layerscape SoC architecture. The QorIQ LS2085A (Fig. 1) is built around an 8 core Cortex-A57 with 4 Mbytes of L2 cache. Each 2 core pair has 1 Mbytes of L2 cache. The system also shares a single 1 Mbyte L3 cache. The two 64-bit DDR4 memory controllers support ECC and have an interleaved bandwidth of 2.1 Gtransfers/s.

Related Articles

- AMD ARMs 64-Bit Servers

- Delivering 64-Bit Arm Platforms

- Architecture Ushers In 64-Bit Computing For Digital Homes

- T4240 QorIQ Processor Pushes OpenVPX 3U SBC To 216 GFLOPS

The LS2 Ethernet switch has an 88 Mbyte/s bandwidth and the on-chip packet processing accelerator has a bandwidth of 20 Mpackets/s. The crypto engine can operate at 20 Gbits/s and the pattern matching engine runs at 10 Gbits/s. Data compression can be handled at rates up to 20 Gbits/s. The system has a secondary, 32-bit DDR4 memory controller just to handle network acceleration support. The combination allows fast, deep packet inspection support making the platforms ideal for software defined networking (SDN) and network function virtualization (NFV). This includes support for standards like OpenFlow.

Network interfaces include eight 1/10 Gbit Ethernet ports plus an addition eight 1 Gbit Ethernet ports. It supports L2 switching on the ports. The IEEE MAC security (MACsec) support can be applied to four of the 1/10 Gbit Ethernet ports.

The PCI Express Gen 3 support can handle SR-IOV (single root-I/O virtualization). Configurations include 1x8, 4x4, 4x1 and 4x1. There is also a pair of SATA 3.0 ports and two USB 3.0 ports with built-in PHYs.

The LS2045A halves the number of cores in the LS2085A. This cuts the amount of L2 cache but it incorporates the same peripheral complement.

Freescale also announced addition Power Architecture QorIQ SoCs that are also based on Layerscape. These include the T4080 with eight, 64-bit, e5500 Power Architecture cores. The T1023 and T1024 utilize one to four cores. The T4080 includes AltiVec vector support. It is pin-compatible with the T4160 and T4240.

These SoCs incorporate a smaller peripheral complement including a single 10 Gbit Ethernet port. They also support Freescale’s QorIQ trust architecture with secure boot, secure debug and tamper detect. The chips also have volatile key storage.

They Layerscape SoCs are run Linux. Freescale provides the open source drivers for the hardware accelerators and other on-chip peripherals.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.