New Design Equations Improve Continuous Mode Interleaved Flyback Converter

Continuous mode interleaved flyback converters (Figure 1) consist of two continuous mode (single switch) flyback converters whose power transistors are turned on at alternate half cycles and whose secondary currents are summed through two rectifling diodes. There are two main operational modes: discontinuous and continuous. Figure 2 shows the continuous mode waveforms. Both modes have identical schematic diagrams and only the output load current and transformer primary inductance determine the mode of operation.

The discontinuous mode does not have a front-end step in its primary current and at turnoff, the secondary current is a decayingtriangle. All the energy stored in the primary during the on-time is completely delivered to the secondary before the next ontime.

With better transient response the discontinuous mode responds more rapidly to sudden changes of load current and input voltage. On the other hand, the larger secondary peak current in the discontinuous mode causes a greater RFI problem. The very large initial spike of secondary current during the turn-off time produces a much more severe noise spike on the output ground bus due to the large di/dt into the output bus. Secondary RMS currents in the discontinuous mode can be up to twice that of the continuous mode. Consequently, larger secondary wire size and output capacitors are needed for the discontinuous mode,

In the continuous mode, the primary current has a front end step. During the transistor off time, the secondary current waveform is a decaying trapezoid with current still remaining in the secondary at the start of the next turn-on. Consequently, there is still energy stored in the secondary at the start of the next turn on.

When the transistor is on, the voltage across the primary oftransformer T1 is VI-VDS, and the core is driven up the hysteresis loop. When the transistor is off, the magnetizing current that is trying to remain constant, reverses the polarity of all voltages.

In the steady state, the volt-second product across the primary during transistor ON time must equal the voltage-second across the primary when the transistor is off:

Primary voltage x tON = secondary voltage x transfer ratio x tOFF

(VI - VDS) tO = (VON + VD + VS) x tOFF x N

where:

- N = Transfer ratio (Np/Ns)

- VI = Minimum input DC voltage

- VS = Voltage drop across load lines

- VDS = Drain - Source voltage at ON time

- VO = Output DC voltage

- VD = Rectifier forward drop voltage

- tON = Primary ON time

In the continuous mode there is no dead time, so tON + tOFF = T.

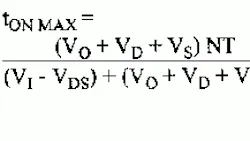

Thus, Equation (1) may be rear ranged as:

Figure 3 shows that output power is equal to the output voltage multiplied by the average of the secondary current pulse, which is:

Substituting tOFF = T - tON in Equation (3):

Equation (4) may be rearranged for ISAV:

From Figure 3, the relationship between average input power PI and the primary current at the center of the ramp IPAV is:

Substituting Pi = P0/η in Equation (5) and rearranging for IPAV provides:

Where η is the converter efficiency.

The step of continuous mode CUIrent begins to appear when the current at the center of the primary ramp IPAV is equal to half the ramp amplitude dIp. That value of Ip is then the maximum peak current at which the converter still is in the discontinuous mode.

Rearranging for dIp provides:

In the discontinuous mode, the voltage across the primary may be expressed as:

Because dt = tON and actual VI is (VI - VDS) by rearranging this equation, we get:

Substituting Equation (7) in (8):

Where PO MIN is the minimum output power at continuous mode or maximum power at discontinuous mode. And η is the efficiency at minimum input voltage. This efficiency is most likely lower than the nominal efficiency of the converter due to higher copper losses and higher switching losses related to higher primary current.

tON is the maximum on-time calculated from Equation (2) at minimum input voltage.

Design Procedure

The magnetic design of an interleaved flyback is very similar to design of a single flyback at half the power. Even when both secondary diodes dump current simultaneously, there is no possibility that one diode can back-bias the other diode and supply all the load current.

To calculate the transfer ratio N:

From Equation (2)

where:

- VI = Minimum input voltage

- VDS = Transistor drain-source ON voltage at maximum input current

- VO = Output DC voltage

- VD = Rectifier forward voltage at maximum output current

- VS = Voltage drop across load leads

- tON = Maximum primary ON time

For an interleaved flyback, agood practice is to make sure that the maximum duty cycle is between 36% to 38%, because most of the current mode controllers do not provide more than 44% duty cycle at high frequencies. If necessary, recalculate the transfer ratio N to make sure maximum duty cycle is 38%.

The primary inductance, Lp is:

where:

- VI = Minimum input voltage

- PO MIN = Minimum output power at continuous mode for one transformer

- η = Efficiency at low input voltage

Air Gap Size

For "C" cores transformer, which have better form factor, the air gap size Lg is [2]:

where:

- Lm = Magnetic path (cm)

- μr = Relative permeability

- A = Core cross section area (cm2)

A proper air gap can reduce the magnetic circuit reluctance by reducing the remanent flux density, thereby increasing ΔB more than ΔH. When the magnetic circuit includes a large air gap, fringing flux in the region of the gap results in a significant increase in the power loss in the local eddy currents. The maximum allowed gap size can be calculated from [2]:

where:

- Bs = Saturation flux density (G)

- DC = Average DC permeability

- Hc = Coercive force

The amount of fringing flux factor, F, is [2]:

where G is derived from “C” core data sheet (cm) (Figure 4)

Lg = Gap size (cm)

Primary turns, Np may be calculated from rearrangement of Ampere’s law:

where F is the fringing flux factor.

For the secondary turns, Ns:

where N is the transfer ratio calculated from Equation (10).

The total flux density, Btotal is a combination of DC flux density and AC flux density (Figure 5).

Btotal = BDC + BAC

The DC flux density may be expressed from Ampere’s law as:

The AC flux density may be expressed as:

where:

- IDC = Average DC current at full output power and low input voltage, which may be calculated from Equation (6) by:

- IAC = Swing current at full output load and low input voltage, which may be calculated by:

Experimental Results

Figure 6 is a simplified schematic of a 200W, continuous mode interleaved flyback converter. It delivers +5v at 40A. The conversion frequency is 260 Hz, which was determined to be a reasonable compromise between size and efficiency. The efficiency at nominal input voltage of 28V measured to be 87.4%.

References

- Product Application Handbook, Unitrode 1993-94.

- Magnetic Core Selection for Transformers and Inductors, W. T. McLyman.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: