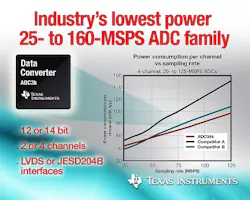

Industry's Lowest-Power 25- to 160-MSPS Analog-to-Digital Converter Family Saves Energy

Texas Instruments expanded its data converter portfolio today with a new family of small, pin-compatible analog-to-digital converters (ADCs) that provide a best-in-class power-to-performance ratio. The ADC3k family includes 12- and 14-bit options in speed grades of up to 160 MSPS with 2 or 4 channels and with LVDS or JESD204B interfaces. The devices support the industrial ambient temperature range of -40C to 85C for use in industrial applications, such as motor control, medical imaging, and portable test and measurement, as well as defense and communications applications, such as software defined radio and MIMO communications.

Key benefits of the ADC3k:

a.. Best-in-class power consumption and power-to-performance ratio: At the fastest sampling rate of 160 MSPS, the devices use only 200 mW/ch, 80 mW/ch less than similar devices, and provide a 30 percent better power-to-performance ratio. Power scales to 44 mW/ch at 25 MSPS.

b.. Large, pin-compatible family: Extensive pin-compatible family scales to meet multi-platform system needs for various sampling rates and channel counts.

c.. Smallest size reduces board space: 4-channel, 160-MSPS devices are half the size of existing devices.

d.. Simplifies board routing: JESD204B variants are compliant with subclass 0, 1, and 2 at up to 3.2 Gbps. They support one lane per ADC output up to 160 MSPS, and one lane per two ADCs for up to 80 MSPS.

e.. Unique performance features: Optional dither and chopper functions can improve spurious free dynamic range (SFDR) and remove 1/f noise, which allows designers to optimize device performance to meet system needs. New amplifier to drive higher performance

The new THS4541, the industry's lowest power consumption rail-to-rail output, fully differential amplifier capable of 850-MHz gain bandwidth (GBW), enables system designers to maximize the performance of their ADC3k device. The THS4541's superior harmonic distortion performance of 123/-130 dBc HD2/HD3 at 1 MHz enables a fully differential AC- or DC-coupled solution for greater flexibility while enhancing the performance of the ADC3k device. When combined, the devices also provide ultra-low power and the smallest analog front end solution at their performance levels.

A TI Designs reference design (TIDA-00294) is available to accelerate high-speed signal acquisition system design. The high-performance, single-ended-to-differential active interface design includes the 12-bit, 4-channel, 50-MSPS ADC34J22 ADC and THS4541. It is optimized for DC-coupled, single-ended input applications, such as motor control, medical imaging, portable test and measurement, and defense munitions. Engineers can use the design methodology for any device in the ADC3k family.

System designers can pair existing or upcoming JESD204B and LVDS ADC3k evaluation modules (EVMs) with the TSW14J50EVM and TSW1405EVM pattern generator and data capture card, respectively, for a low-cost evaluation system.

For designers using Altera's Cyclone V SOC FPGA, Dallas Logic has developed a 4-channel, 12-bit, 50-MSPS ADC module that integrates with Altera's High Speed Mezzanine Card (HSMC) standard. The DEV-ADC34J22 features the ADC34J22 and THS4541, along with TI's LMK04828 clock jitter cleaner, and provides single-ended DC-coupled inputs on two of the four channels. The module is available for purchase from Arrow for US$199.

The ADC3k family will include 32 pin-compatible devices by the end of 2015 with speed grades ranging from 25 MSPS to 160 MSPS. The family comes in a 7-mm by 7-mm QFN package with the exception of the 4-channel LVDS versions, which use an 8-mm by 8-mm QFN.