The term “low power” is now so endemic, it has lost a lot of its impact and some of its meaning. From an MCU manufacturer’s point of view, low power is relative to the competition. Not all Cortex-M4-based MCUs, for example, operate within the same power envelope.

To really deliver low power, independent device manufacturers (IDMs) must develop their own low-power technologies and methodologies that they can apply to the Cortex-M4 intellectual property (IP). Atmel’s low-power solution, for instance, is picoPower.

Meeting Requirements

When an MCU is designed for low power, it must deliver across a range of use cases. Measuring power isn’t straightforward under the best of conditions, so being able to rely on the entire architecture to deliver low-power operation under all conditions is essential. Benchmarking MCUs for power largely depends on two states of operation: dynamic and static.

Under dynamic conditions, the frequency of operation clearly has an impact, as power is “nominally” only consumed in a CMOS circuit when there is a logic transition. Reducing the frequency, therefore, lowers the transitions per second, but doesn’t address the number of times a transistor must switch to achieve a given task.

Voltage has an exponential impact on power consumption. Reducing the supply voltage delivers greater power savings than scaling the frequency alone. Operating from a lower supply voltage isn’t as simple as lowering the clock frequency, however. It must be “designed in” at the process level.

Static power is consumed when the CMOS gates are supposed to be in a quiescent state. While this should, in theory, be zero, in practice it is impossible to create a transistor with no leakage current in modern geometries.

In general, the smaller the geometry is, the greater the leakage current. Therefore, as more transistors are integrated in a device, the overall potential static leakage current will increase. By developing low-leakage transistors, a proprietary process like picoPower can successfully address these issues and get the leakage close to the theoretical zero without sacrificing performance.

The fastest and most frequently switching transistors in an MCU will be found in the core’s RAM and the core itself. So during all the time that the core and its subsystem are active, it will dissipate the greatest amount of system power. That’s why sleep modes are now ubiquitous among MCUs.

ARM developed the Cortex-M4 to support two sleep modes, each of which turns off a greater or lesser degree of system clocks. IDMs choose how to implement their own sleep modes, but they all essentially require the core to halt and store system-critical information in registers and RAM, ready to be reinstated when exiting sleep mode. This all takes time, and in a typical MCU application, time is synonymous with responsiveness.

As a result, low power goes far beyond a transistor’s switching characteristics. It is a direct result of the overall system architecture. Only by approaching the architectural design from this systemic viewpoint can an IDM truly develop a low-power solution.

1. Atmel’s SAM4L achieves up to 28 CoreMark/mA when using the IAR Embedded Workbench, version 6.40.

Better Results

By addressing all aspects of power consumption, IDMs are better able to design an MCU that offers true low-power operation. Implementing a Cortex-M4 in a low-leakage process will, of course, result in lower system power than if it were implemented in a high-performance process.

But if the system design is entirely core-centric, even the most mundane tasks likely will require the core’s intervention. For example, a simple interrupt service routine, even where no action is taken, would require the core, flash, and other system modules to be fully woken from a sleep mode.

Waking a high-performance core like the Cortex-M4 and its entire subsystem from deep sleep only to execute a service interrupt routine or some other simple task would take considerably longer than the time needed to process the actual task. This not only would consume a significant amount of valuable system power, but most of it would be used just in waking the system.

It follows that through a holistic approach that adopts low-power techniques complementary to the core, an IDM can develop and implement features that extensively use low-leakage transistors in the core and peripherals while reducing the time spent processing. Consequently, these techniques can maximize low-power operation.

This holistic approach is proving to be the most relevant and effective way for manufacturers to optimize for power. The degree to which it is employed is what really differentiates IDMs within the Cortex-M4 sphere.

Before static power became a major factor in system design, active power was possibly the only design parameter that concerned most engineering teams. IDMs like Atmel have a long history of delivering MCUs that offer more performance at lower active power. This legacy isn’t by accident.

One aspect of maintaining low active power is finding the most efficient way of moving in and out of sleep modes. The faster the system clock can be re-established, the faster the core can complete its task and the less active power used.

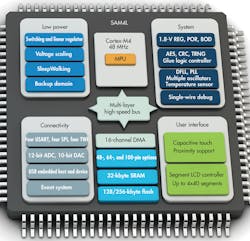

Further to this, for example, Atmel implements features that can operate independently of the core. Intelligent, autonomous peripherals can process inputs and outputs independently of the CPU. Running off a dedicated clock, this approach lets the core remain in sleep mode for longer. Through carefully architected inter-communication features, peripherals also can exchange data using shared buses, enabling them to make intelligent decisions based on external stimuli without having to wake the core.

Enabling peripherals to operate autonomously is now recognized as a key addition to low-power operation. However, it is again crucial that the implementation is integral to the overall system architecture. A fast response time to the point of real-time operation is essential if peripherals are to manage tasks normally handled by a high-performance core.

Current Applications

For example, the Peripheral Event System in Atmel’s SAM4L is independent of both the CPU and its clocking system. With its own access control to the real-time clock, it can continue operating when the CPU and the system clock are effectively “off.”

Atmel’s picoPower approach to low power was first used in the 8-bit AVR XMEGA family and continues with Atmel’s first picoPower Cortex-M4 device, the SAM4L. It is used to address the three key areas of power consumption within an MCU: sleep mode, active mode, and wakeup times.

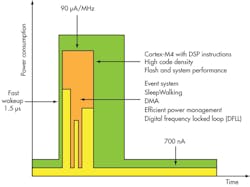

Within the SAM4L, picoPower lets the device achieve a very low-active-mode power consumption of 90 μA/MHz, which is achieved in part through the development of an ultra-low-power buck regulator that not only reduces the voltage for most frequently switching gates, but also does it with high efficiency.

2. In sleep mode, the SAM4L draws as little as 0.5 μA with the real-time clock still running and with a wakeup time of less than 2 μs.

Thanks to the holistic low-power design approach that also includes the process development, the SAM4L can operate down to 1.62 V. It consumes as little as 1.5 μA in wait mode, with full RAM retention.

Bundled with an unrivalled wakeup time of less than 1.5 μs, the SAM4L boasts the lowest total power consumption. In sleep mode, it draws as little as 0.5 μA with the real-time clock still running and with a wakeup time of less than 2 μs.

When selecting a Cortex-M4 based microcontroller for a new design, embedded developers should consider checking their desired devices against an industry benchmark such as the CoreMark standard from the Embedded Microprocessor Benchmark Consortium (EEMBC). The CoreMark standard is a measure of exactly how much power a device takes to execute a standard set of functions.

MCU vendors continue to strive to achieve lower power consumption and device optimizations. Balancing the needs of the power budget without compromising on MCU performance and application responsiveness is key to these advances.

About the Author

Andreas Eieland

Product Marketing Manager

Andreas Eieland, MSc, is product marketing manager for 8-bit AVR products at Atmel, a position he has held since 2007. He previously worked as an application engineer at Atmel’s AVR Products Center. He holds a master of science degree from the Norwegian University of Science and Technology.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: