40A Converter Output Stage Emulates DrMOS with Internal Power MOSFETs

The integrated PowIRstage® IR3553 provides the power output stage for a 40 A synchronous buck converter, or when used in a multiphase configuration, each phase can carry 40A. This multichip module contains the gate drivers, control MOSFET, synchronous MOSFET, and integrated Schottky diode (Fig. 1). The IR3553 is electrically compliant with Intel’s DrMOS V4.0, and contains the same functions (driver, MOSFETs, Schottky depending on the vendor), but comes in a unique, thermally enhanced package. An advantage of the IR3553 package is that the copper clip packaging provides lower parasitics than wirebonded MOSFETs. This optimizes the IR3553 for PCB layout, heat transfer and driver/MOSFET timing.

The IR3553 includes a custom-designed gate driver and MOSFET combination that enables higher efficiency at the lower output voltages required by CPU, GPU and DDR memory designs. It can accept a 4.5V to 15V input (VCC pin 3) and provides an output from 0.25V up to VCC-2.5V. Housed in 4 x 6 x 0.9 mm, 25-pin PQFN package, it is lead-free, RoHS compliant, and allows dual-sided cooling.

The IR3553’s 1.0MHz (max.) switching frequency (fSW) enables high performance transient response while allowing smaller size output inductor, input and output capacitors. It exhibits an efficiency greater than 90% with a 1.2V output (Fig. 2). Its PCB footprint is similar to the IR3550 (60A) and the IR3551 (50A). All three devices can be placed onto the IR3550 pad layout.

The IR3553 is intended for use with a PWM controller input that is compatible with 3.3V logic and is 7V tolerant. Its PWM controller input accepts 3-level tri-state signals. When the PWM input is high, the synchronous MOSFET turns off and the control MOSFET turns on. When the PWM input is low, the control MOSFET turns off and the synchronous MOSFET turns on. By floating the PWM pin, built-in resistors pull the PWM pin into a tri-state region centered around 1.65V.

Body-Braking Mode

The IR3553 can implement Body-Braking, an operation that turns the two MOSFETs off. When the synchronous MOSFET is off, the higher voltage across the Schottky diode in parallel helps discharging the inductor current faster, which reduces the output voltage overshoot. Body-Braking can be used either to enhance converter transient response after load release or to provide a high impedance output.

There are two ways to place the IR3553 in Body-Braking mode, either by controlling the BBRK# pin directly or through a PWM tri-state signal. Both signals are usually from the PWM controller.

Pulling BBRK# (pin 20) low forces the IR3553 into Body-Braking mode rapidly. Releasing BBRK# forces the IR3553 out of Body- Braking mode quickly.

If the BBRK# input is always high, Body-Braking activates when the PWM input (pin 19) enters the tri-state region. Compared to pulling down the BBRK# pin directly, Body-Braking response is slower due to the hold-off time created by the PWM pin parasitic capacitor with the pull-up and pull-down resistors on the PWM pin. For best performance, ensure that the PWM pin has less than 100pF of parasitic capacitance.

The BBRK# pin should be pulled up to VCC if the feature is not used by the PWM controller. Use a low value pull-up resistor or a direct connection to VCC.

Synchronous Diode Emulation Mode

An additional feature of the IR3553 is the synchronous diode emulation mode, which enables increased efficiency by preventing negative inductor current from flowing in the synchronous MOSFET.

To ensure the diode emulation mode is properly set, the BBRK# pin must be toggled low at least once after the VCC passes its UVLO (under-voltage lockout) threshold during power up (3.3V minimum and 3.7V typical). A digital signal from the PWM controller can also be used to set the diode emulation mode. The BBRK# signal can either be pulled low for at least 20ns after the VCC passes its UVLO threshold, or be pulled low before VCC power up and then released after the VCC passes its UVLO threshold. Once the diode emulation mode is set, it cannot be reset until the VCC power is recycled.

Current Sense Amplifier

An internal high speed differential current sense amplifier has a gain of 32.5 (nominal). Its output, IOUT, is referenced to REFIN (pin 22), which is usually connected to a reference voltage from the PWM controller. The current sense amplifier can accept positive differential input up to 25mV and negative input up to -10mV before clipping. The output of the current sense amplifier is summed with the reference voltage and sent to the IOUT pin (23).

The input offset voltage is the primary source of error for the current signal. To maintain an accurate current signal, the current sense amplifier continuously calibrates itself, and its input offset is within ± 450µV. This calibration algorithm may create a small ripple on IOUT with a frequency of fsw/128.

If the IR3553 current sense amplifier is required, connect its output, IOUT, and the reference voltage REFIN to the PWM controller and connect the inductor sense circuit. If the current sense amplifier is not needed, tie CSIN+(2), CSIN-(1) and REFIN pins to LGND (21) and float the IOUT pin.

The IR3553 is capable of creating output voltages above the 3.3V recommended maximum output voltage as there are no restrictions inside the IR3553 on the duty cycle applied to the PWM pin. However, if the current sense feature is required, the common mode range of the current sense amplifier inputs must be considered. Also, the output current rating of the device will be reduced as the duty cycle increases. In very high duty cycle applications sufficient time must be provided for replenishment of the bootstrap capacitor for the control MOSFET drive.

There is a zero current detection circuit in the IR3553 that is independent of the current sense amplifier and therefore still functions even if the current sense amplifier is not used. An offset is added to the diode emulation comparator so that a slightly positive output current in the inductor and synchronous MOSFET is treated as zero current to accommodate propagation delays, preventing any negative current flowing in the synchronous MOSFET. This causes the Schottky diode in parallel with the synchronous MOSFET to conduct before the inductor current actually reaches zero, and the conduction time increases with output inductor inductance.

Fig. 3 shows the IR3553 safe operating area with the case temperature controlled at or below 125°C. Test conditions are:

VIN = 12V

VOUT = 1.2V

ƒSW = 400kHz

L = 150nH (0.29mΩ)

VCC = 7V

TAMBIENT = 0°C to 90°C, no heat sink

A phase fault circuit looks at the switch node with respect to ground to determine whether there is a defective MOSFET in the phase. The output of the phase fault signal is high during normal operation and is pulled low if there is a fault. Each driver monitors the MOSFET it drives. If the switch node is less than a certain voltage above ground when the PWM signal goes low or if the switch node is a certain voltage above ground when the PWM signal rises, it produces a fault signal. The phase fault signal asserts if there are a number of consecutive faults.

A Thermal flag circuit monitors the IR3553ís temperature. If the temperature goes above a threshold limit (150°C typical) the PHSFLT# pin (18) goes low after a maximum delay of 100µs.

The PHSFLT# pin can be pulled low by either the phase fault circuit or the thermal flag circuit. If PHSFLT# is not used it can be floated or connected to LGND.

DCR Sensing

Inductor current can be sensed by connecting a series resistor and a capacitor network in parallel with the inductor and measuring the voltage across the capacitor, as shown in Fig. 1. Usually the resistor RCS (R2) and capacitor CCS (C4) are chosen so that the time constant of RCS and CCS equals the inductor time constant, which is the inductance L over the inductor DCR (RL). If the two time constants match, the voltage across CCS is proportional to the current through L, and the sense circuit can be treated as if only a sense resistor with the value of RL was used. The mismatch of the time constants does not affect the measurement of inductor DC current, but affects the AC component of the inductor current. (DCR is the inductor’s DC resistance.)

The advantage of sensing the inductor current versus high side or low side sensing is that actual output current being delivered to the load is obtained rather than peak or sampled information about the switch currents. The output voltage can be positioned to meet a load line based on real time information. This is the only sense method that can support a single cycle transient response. Other methods provide no information during either load increase (low side sensing) or load decrease (high side sensing).

If the IR3553 is used with inductor DCR sensing, care must be taken in the printed circuit board layout to make a Kelvin connection across the inductor DCR. The DC resistance of the inductor is utilized to sense the inductor current. Usually, the resistor RCS and capacitor CCS in parallel with the inductor are chosen to match the time constant of the inductor, and therefore the voltage across the capacitor CCS represents the inductor current.

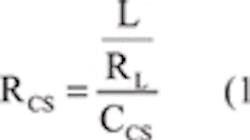

Measure the inductance, L, and the inductor DC resistance, RL. Pre-select the capacitor CCS and calculate RCS as:

Where:

RCS = Current sense resistor (R2 in Fig. 1)

CCS = Current sense capacitor (C4 in Fig. 1)

At least two 10µF 1206 ceramic capacitors and one 0.1µF 0402 ceramic capacitor are recommended for decoupling the VIN to PGND connection. Adding more capacitance with lower ESR and mounted with low inductance routing improves efficiency and reduces system noise, especially in single-phase designs or during high current operation.

A 0.1µF to 1µF ceramic decoupling capacitor is required at the VCC pin. It should be mounted on the same side of the PCB as the IR3553 and as close as possible to the VCC and PGND (pin 4). Low inductance routing between the VCC capacitor and the IR3553 pins is recommended.

Related Articles

Designing with DrMOS Part 1: Concept and Features

Designing with DrMOS, Part II: Application Guidelines

About the Author

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: