Model Current-Mode Control With Ease and Accuracy

Current-mode control (CMC) is widely used in dc-dc converters for high-performance applications. In spite of its implementation simplicity, the dynamics are complicated and designing the control loop can be challenging. Many research efforts in the last two decades have refined dynamic models that capture the most relevant aspects of the controller behavior. Today's designers can choose from a vast pool of theoretical resources when developing a CMC solution.

A new model is being proposed that maximizes the advantages of the most popular model, while improving on its weaknesses. This model is based on already existing models but outperforms them in the design practice.

Eliminating Inductor Dynamics

The main idea behind CMC is that the inductor can be turned into a current source, thus eliminating the dynamics of the inductor in the loop.[1] The controller sets a current reference and a fast inner-loop follows this reference cycle by cycle.

A typical implementation for a buck converter is shown in Fig. 1.[2] This is the so-called peak CMC, because the inductor peak current follows the reference, as shown in the Fig. 2 waveforms. (Note that the inductor current shown in Fig. 2 corresponds to the sensed current, i.e., RI × IL) There is an outer voltage loop with an error amplifier that compensates for the dynamic response of the output voltage. The current loop is an inner loop that provides tight control on the peak inductor current.

There are similar architectures for average CMC and valley CMC, although they are not as popular.[3-4] The compensation ramp shown in Fig. 1 is introduced to avoid subharmonic oscillations for duty cycles larger than 0.5.[2] The slope of the compensation ramp (SE in Fig. 2) plays an important role in the response of the system, as will be shown later.

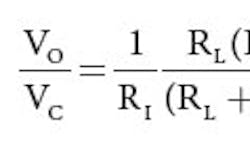

Assuming that current tracking is perfect, the system effectively becomes a first-order model. The inductor current can be assumed to be equal to the reference current (VC/RI in Fig. 1). The control-to-output transfer function for a buck converter becomes:

where RC is the ESR of the output capacitor.

Because this first-order transfer function is very easy to compensate, the design of the error amplifier is ideally simplified.

The assumption that current tracking is perfect is only valid for slow variations of the control signal, thus this model is only meaningful at low frequencies. If there is a need to push the bandwidth of the closed-loop system to frequencies above approximately one-tenth of the switching frequency, then a more detailed description of the dynamics of the current modulator is needed.

Over the years, many researchers have proposed models for CMC that take into account the dynamics at frequencies approaching the switching frequency.[5-11] These models are developed under different assumptions about two main aspects of the loop dynamics.

The first assumption is the duty-ratio constraint that relates the duty cycle to the average values of the programmed current, the inductor current, the input voltage and the output voltage.[12] Typical for this constraint are the use of a piecewise linear inductor waveform, in which the slopes may be constant or may change with the input and output voltages, and the definition of average inductor current, which can be computed as in steady-state or transient operation.

The second assumption is the sampling effect inherent to the modulation method. Typical for the sampling effect are the inclusions of either a fixed delay or a zero-order hold effect. It was noted that the modulator creates frequency components at the output that were not present at the input and that, for perturbations above one-tenth of the switching frequency, the additional components at the output are significant.[12] This fact, together with the time-varying nature of the modulator, poses a warning against the validity of linear time-invariant (LTI) models for characterizing the behavior of the current loop at high frequencies. However, practice has demonstrated that LTI models are very useful for the design process, because they can capture enough information as to predict the stability and performance of the controller.

A unified model for different current-mode architectures and using general gain parameters was presented by Robert Sheehan of National Semiconductor (“A New Way to Model Current-Mode Control,” June 2007, Power Electronics Technology).[13-14] The unified model is consistent with the general models derived and can be extended to emulated CMC using sampling and hold techniques.[8, 11]

A very popular and widely accepted model was first introduced by Raymond B. Ridley (“A New, Continuous-Time Model for Current-Mode Control,” IEEE Transactions on Power Electronics, 1991, vol. 6, no. 2, pp. 271-280).[8] That model is derived using a sampled-data analysis and takes into account the sampling effect of the modulator by introducing a zero-order hold. As a result, both low-frequency behavior and high-frequency subharmonic oscillations can be predicted. The inner current loop is then modeled as shown in Fig. 3:

where FM is the modulator gain, SN is the on-time slope of the sensed inductor waveform, namely RI × VI/L in a buck converter, SE is the slope of the compensation ramp and TS is the switching period.

where FI is the approximate transfer function (ignoring parasitics and assuming the output voltage is constant) from the duty cycle to the inductor current and the sampling gain is:

A rational approximation of Eq. 4 can be computed using a Padé approximation of order (2, 2) of the exponential function.[15] This is useful for analysis purposes and for using some simulation tools that only allow rational transfer functions. The resulting sampling-gain approximation becomes a two-zero function given by:

where ωN = π/TS and QZ = -2/π.

It has been noted in literature (Mayer and King, The University of Toledo) that some of the assumptions yield an inaccurate dc gain in the loop-transfer function.[8, 16] This was confirmed in practice by the authors. In the following section, the source of this inaccuracy is identified and a new model with an accurate dc gain is proposed.

Proposed New Model

The new model proposed here incorporates most of the assumptions of Ridley's continuous-time model with one small but important difference in the computation of the average inductor current.[8] From Fig. 2, the sensed peak current (IP) can be expressed in terms of VC as:

and in terms of the average sensed inductor current (IL) as:

(Note that the average inductor current is computed as in steady-state operation, under the assumption that the inductor current returns to the same valley value at the end of the cycle.)

From Eqs. 6 and 7:

Then, under the assumption that slope SN is constant, the modulator gain can be expressed as:

This expression is different from the one used in Ridley's continuous-time model.[8] Actually, this modulator gain was reported even earlier (Middlebrook, Caltech), but in the context of a different derivation method.[5-6]

Following Ridley's derivation, a perturbation in the command voltage is introduced and the variation in the inductor current is computed (Fig. 4).[8] The variation in the inductor current is approximated by the sampled waveform is(k). Then, the closed-loop-transfer function between the command voltage Vc and the sampled inductor current (is) can be computed in the discrete-time domain, resulting in:

The equivalent continuous-time transfer function can be obtained as:

where a = (SF - SE)/(SN + SE).

In Fig. 3:

The new sampling gain HE(s) is computed as:

A rational approximation can be obtained applying the same Padé approximation[8], resulting in:

where ωN = π/TS and QZ = -(SN/SF + 1)2/π.

This expression is almost equal to the one in Eq. 5 with a slight difference.[8] Although both the dc gain and the frequency of the double zero are the same, the quality factor is different.

Comparison of Models

The loop-transfer function of both the proposed new model and Ridley's model are compared with that obtained from a switched model simulated with the SIMetrix/SIMPLIS software tool.[8, 17] The advantage of the SIMPLIS simulator is that it can compute a periodic operation point and introduce perturbations to obtain a small-signal transfer function around said operation point, thus computing numerically the transfer function. The former models were simulated using SIMetrix SPICE and performing a traditional ac analysis.

For this example, a buck converter with Fairchild's FAN2013 controller was used. The FAN2013 is a 2-A low-voltage current-mode synchronous pulse-width-modulated buck regulator designed for applications like hard-disk drives, set-top boxes, notebook computers and communications equipment. The circuit parameters used in these simulations are listed in the table.

The results are shown in Fig. 5. The new model proposed here shows a more accurate dc gain and improved mid-frequency phase characteristics than Ridley's model. References to prior work mentioned in this article are listed in the online version at www.powerelectronics.com.

Resources

- C.W. Deisch, “Simple switching control method changes power converter into a current source,” IEEE PESC, 1978, pp. 300-306

- R.W. Ericksson and D. Maksimovic, Fundamentals of Power Electronics, Second Edition, Springer, 2001

- L.H. Dixon, “Average current mode control of switching power supplies,” Unitrode Power Supply Design Seminar, 1988.

- R. Rossetti and S.R. Sanders, “Valley Design Techniques Outperform Peak Current Mode Approach for CPU Supplies,” Power Electronics Technology, July 2001.

- S. Hsu, A. Brown, L. Rensink, and R. Middlebrook, “Modeling and analysis of switching dc-to-dc converters in constant-frequency current-programmed mode,” IEEE PESC, 1979, pp. 284-301.

- R. Middlebrook, “Topics in multiple-loop regulators and current-mode programming,” IEEE PESC, 1985, pp. 716-732.

- G.C. Verghese, C.A. Bruzos, and K.N. Mahabir, “Averaged and sampled-data models for current mode control: a re-examination,” IEEE PESC, 1989, pp. 484-491.

- R.B. Ridley, “A new, continuous-time model for current-mode control,” IEEE Trans. on Power Electronics, vol. 6, no. 2, April 1991, pp. 271-280.

- R. Tymerski and D. Li, “State space models for current programmed pulse width modulated converters,” IEEE PESC, 1992, pp. 337-344.

- C.P. Schultz, “A unified model of constant frequency switching regulators using multiloop feedback control,” PCIM, 1993, pp. 319-329.

- F. Tan and R. Middlebrook, “A unified model for current-programmed converters,” IEEE Trans. on Power Electronics, vol. 10, no. 4, pp. 397-408, 1995.

- D.J. Perreault and G.C. Verghese, “Time-varying effects and averaging issues in models for current-mode control,” IEEE Trans. on Power Electronics, vol. 12, no. 3, pp. 453-461, May 1997.

- R. Sheehan, “A new way to model current-mode control - Part one,” Power Electronics Technology, May 2007.

- R. Sheehan, “A new way to model current-mode control - Part two,” Power Electronics Technology, June 2007.

- S. Hamilton, An Analog Electronics Companion: Basic Circuit Design for Engineers and Scientists, Cambridge University Press, 2003, Section 3.14.

- E.A. Mayer and R.J. King, “An improved sampled-data current-mode-control model which explains the effects of control delay,” IEEE Trans. on Power Electronics, vol. 16, no. 3, May 2001.

- Catena Software Ltd., http://www.catena.uk.com/

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: