An Unconditionally Stable Linear Voltage Regulator

We recently derived the phase margin of a linear regulator from its output impedance measurement. The output impedance was described in terms of a passive series inductor and resistor and sometimes also including a parallel resistance. The phase margin was evaluated through its relationship with the Q resulting from this network and the output capacitor, including the parasitic ESR of the capacitor.

Understanding this relationship leads us to the simple solution to the stability criteria – don’t allow the use of an output capacitor for your regulator application. This is the seemingly simple solution, though not without significant ramifications. For example, what about the decoupling requirements of the high speed integrated circuits and op amps connected to the regulator?

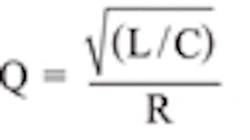

If we define the Q of the regulator equivalent network as:

Where:

L = Effective inductance of the regulator

C = Output capacitance

R = Total series resistance of the circuit,

By including the resistance of the regulator and the ESR of the capacitor we can see there are several other possible solutions.

If the circuit resistance, R, is infinite then the circuit could be unconditionally stable

If the effective inductance is reduced to zero

If the capacitance is infinite (assuming non-zero resistance).

Having three parameters offers us three solutions. Now the evaluation becomes a bit more complex.

It is obviously not feasible to have infinite resistance, as this would lead to a maximum output current of zero, nor is it possible to achieve a circuit that has infinite capacitance or zero inductance – or is it?

In the simplest voltage regulator, a single pass transistor is used as an emitter follower with an op amp comparing the output voltage to a fixed reference voltage. The dynamic resistance of the transistor, is:

Where:

IE = Output current

Therefore, the transistor resistance is a function of the output current. The conversion from resistance to inductance is the result of the single pole transfer function of the amplifier. Evaluating the closed loop impedance of the regulator can be accomplished using the relationship

Where:

ZCL = Closed loop impedance

ZOL = Open loop impedance

T = Vector control loop gain

If T is single pole transfer function, then we can evaluate the form of the output impedance as:

Where:

k = low frequency loop gain

a = Op amp pole frequency

For gains larger than unity, we can simplify this as:

Having s in the numerator, it is now obvious that the resistance RD is transformed to an inductance for frequencies greater than a and we can also see that the inductance is a product of RD while RD is an inverse product of IOUT such that the inductance decreases with both increasing frequency and also with increasing load current.

This leads us to one possible solution for a zero inductance regulator – create a loop having an infinite gain bandwidth product. An infinite bandwidth would allow the regulator to present a very low impedance, over a wide frequency range, allowing low value decoupling capacitors and very small values of series resistance to result in stable solutions.

Is it practical to achieve an infinite or nearly so bandwidth regulator? Many of today’s high speed op-amps offer low noise and very wide bandwidth, while being stable at unity gain. While this solution may seem extreme, it is far from impractical.

HIGH BANDWIDTH

The following example, shown in Fig. 1, demonstrates the performance of a custom built regulator with a bandwidth of approximately 300MHz. Certainly, 300MHz is not infinite, but arguably such a bandwidth is quite high by present standards. Higher bandwidths are certainly possible with the availability of opamps and transistors well into the GHz range, though the PCB layout and secondary stability impacts become more complex at these higher frequencies.

The proposed high bandwidth solution makes use of UHF bipolar RF transistor technology and high RF or MMIC op amps to trade silicon for capacitors. While the silicon may be more expensive, the reduction or elimination of output capacitors improves physical density and also improves reliability and stability. The circuit still allows the use of decoupling capacitors, where necessary, allow the optimization of stability as a tradeoff for ESR or series resistance [1].

The output impedance of our example regulator was measured using an OMICRON-Lab Bode 100 and a Picotest J2111A Current Injector. The results are shown, in comparison to a typical LM317 voltage regulator, in Fig. 2. Both regulators are measured in the same test setup, using a daughter board and the Picotest Voltage Regulator Test Standard (VRTS) kit with no output capacitor. A 25mA constant current load is presented by the J2111A Injector to the regulator.

The resulting output impedance of our high bandwidth regulator is approximately a factor of 50 lower than a typical LM317 Regulator. The effective output inductance, at an output current of 25mA, is approximately 70nH. In this circuit, a 0.1uF capacitor would offer a peak output impedance of 1 Ohm and would be very stable for total series resistance greater than 1 Ω. A 1uF ceramic capacitor results in a 0.1 Ω peak output impedance, with very stable performance for all values of total series resistance greater than 0.1 Ω. The typical FPGA circuit generally requires a peak impedance of less than 100 mΩ, which is attainable with very small capacitors.

A high speed small signal step response, again using the J2111A is shown in Fig. 3. The pulse load is 500mA, 200ns wide with 20ns rise and fall times and a 1.2MHz repetition frequency. The MDO4104-6 is used to display both the time domain result and the spectral content of the pulse load simultaneously. The spectral plot shows that the load current has valid harmonics beyond 50MHz, while the upper trace shows the well behaved voltage response.

Fig. 4 shows a comparison between the LM317 and the proposed high bandwidth regulator, both with a 10uF X7R output capacitor. Note that the LM317 result has a very high Q impedance, related to poor stability, while the high bandwidth regulator maintains a low impedance. Note that above 200kHz the impedance is dominated by the PCB trace reflecting an inductance of approximately 65nH.

Fig. 5 shows a PSRR comparison between the LM317 and the proposed regulator without an output capacitor. The 500kHz dip in the high bandwidth regulator is not the bandwidth, but a resonance in the reference circuit, which could be improved without much effort. In general, the high bandwidth regulator provides nearly 40dB improvement in PSRR. Alternate op amps could improve the low frequency PSRR even further.

While absolute unconditional stability may not be an attainable goal, our proposal afor a linear regulator design can achieve very stable performance with a very wide range of load capacitance and load current, while offering very low output impedance. In many low current applications, the use of an output capacitor may not be necessary for regulators with the characteristics noted here. The resulting regulator circuits can also be smaller, due to the use of much smaller output capacitors.

References

Sandler, Steven,” Simple Method to Determine ESR Requirements for Stable Regulators,” Power Electronics Technology, August 2011.

Related Articles

Monolithic Regulators Migrate to Higher Voltages

Low-Voltage LDO Regulators Power Portable Gear

About the Author

Steve Sandler

Steve Sandler is the founder and chief engineer of AEi Systems LLC and the president of Picotest. At Picotest he is responsible for signal injector product development, as well as the overall operation of the test equipment company.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: