MOSFET Selection For Switching Power Supply Systems

MOSFET selection for DC-to-DC switching controllers can be a complicated process. It is not sufficient to merely look at the voltage and current ratings for a MOSFET. A balance between low gate charge and RDS(ON) must be achieved in order to keep the temperature of the MOSFET within specification. This situation becomes more complicated within a multiple load power supply system. On-line design tools such as Texas Instruments’ WEBENCH® Power Architect can ease this process and allow the user to make decisions based on efficiency, footprint and cost to achieve desired design goals for MOSFET controller designs.

DC-to-DC switching power supplies are commonly used in modern day electronic systems for their high efficiency. An example of a step-down (or buck) synchronous switching regulator with a high side FET and a low side FET is shown in Fig. 1. In this configuration, the FETs are switched on and off according to a duty cycle set by the controller in order to achieve the desired output voltage. The equations for duty cycle for a buck regulator are:

Duty Cycle (High side FET) = VOUT/(VIN × Efficiency) (1)

Duty Cycle (Low side FET) = 1 - DC (High side FET) (2)

The FETs may be integrated into the same chip as the controller, which provides the simplest solution. But in order to provide high current capability and/or to achieve the highest efficiency, the FETs need to be kept external to the controller. This allows the greatest heat dissipation since it physically separates the FETs from the controller and it also gives the greatest flexibility in selecting the proper FETs for the job. The disadvantage is that the FET selection process can be difficult since there are many factors to consider.

A typical question is “Why won’t this 10A FET work for my 10A Design?” The answer is that the 10A rating doesn’t necessarily apply to all designs. Factors that need to be considered in FET selection are the voltage rating, ambient temperature, switching frequency, drive capability of the controller, and heat sink area. The key issue is that the FETs may get too hot and burn up if the power dissipation is too high and the heat sinking is inadequate. We can estimate the junction temperature of a FET using the θJA, or thermal resistance, of the package/heat sink, the power dissipated in the FET and the ambient temperature:

TJ = θJA × PdissFET + TA (3)

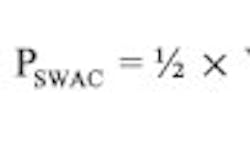

This requires calculation of the power dissipation in the FETs. The power dissipation can be broken down into two main areas, AC and DC losses. These losses can be calculated using:

Where:

PSWAC = AC losses

VDS = Voltage across FET

IDS = Load current

tRISE = FET rise time

tFALL = FET fall time

TSW = Switching time period of controller (1/switching frequency

DC losses: PswDC = RDS(ON) * IOUT * IOUT * Duty cycle (5)

Where:

PSWDC = DC losses

RDS(ON) = FET on resistance

IOUT = Load current for a buck topology

D = Duty cycle

Other loss mechanisms are due to output parasitic capacitance, gate losses, and body diode losses due to conduction during the dead time for the low side FET, but we will focus on the AC and DC losses in this discussion.

The AC switching losses occur during the transition between the switch being on and off, when the voltage and current through the switch are both non-zero. The highlighted areas in Fig. 2 show this. According to Equation (4), one way to reduce these losses is to reduce the rise and fall times of the switch. This can be done by choosing a FET with lower gate charge. Another factor is the switching frequency. The higher the switching frequency, the greater the percentage of the switching period time is spent in the rise and fall transition regions as shown in Fig. 3. Thus, higher frequency means greater AC switching loss. So, another way to lower AC losses is to lower the switching frequency, but this requires a larger and usually more expensive inductor to keep the peak switch current within specification.

DC losses occur when the switch is in the on state and are due to the RDS(ON) of the FET. This is a fairly straightforward I2R loss mechanism as shown in Fig. 4. However, this is complicated by the fact that the RDS(ON) varies with the FET junction temperature. So, to accurately determine the RDS(ON) an iterative process must be used which takes into account the temperature rise of the FET using Equations (3), (4) and (5). The easiest way to reduce DC losses is to select a FET with low RDS(ON). Also, DC losses are proportional to the percentage on time for the FET which is the duty cycle of the controller for the high side FET and 1 minus the duty cycle for the low side FET as was previously mentioned. As is shown in Fig. 5, longer on times mean greater DC switching losses, thus, reducing DC losses can be accomplished by reducing the on time/duty cycle of the FET. The designer may be able to change the duty cycle if the input voltage can be changed, for example if an intermediate DC voltage rail is being used.

GATE CHARGE VS. RDS(ON)

The simple solution is to pick a FET with both low gate charge and low RDS(ON), however, there is a characteristic tradeoff between these two parameters, which is shown in Fig. 6. Low gate charge usually means smaller gate area/fewer transistors in parallel and thus higher RDS(ON). On the other hand, low RDS(ON) is normally brought about by using larger/more parallel transistors, which results in more gate charge. This means the FET selection must balance these two competing specifications. Also, the cost must be taken into account.

For designs with low duty cycle meaning the input voltage is high, the high side FET is mostly off so DC losses are low. But the high voltage across the FET results in high AC losses so a FET with low gate charge can be chosen, even if the RDS(ON) is high. The low side FET is mostly on, but AC losses are minimal. This is because the voltage across the low side FET during turn on/turn off is only due to the FET body diode, which is very low. Thus a FET with low RDS(ON) needs to be selected and the gate charge can be high. This is shown in Fig. 7.

If we lower the input voltage, we get a high duty cycle design where the high side FET is mostly on which is shown in Fig. 8. In this case, the DC losses will be high and low RDS(ON) is required. Depending on the input voltage, AC losses may not be as important, but still not as low as for the low side FET. Thus, moderately low gate charge may still be required. This requires a compromise between low RDS(ON) and low gate charge. For the low side FET, the on time is minimal and AC losses are low, so the FET selection can be made on the basis of price or footprint instead of RDS(ON) and gate charge.

DUTY CYCLE TRADEOFFS

Assuming that for a point-of load (POL) regulator, we have the ability to specify the nominal input voltage from an intermediate voltage rail, what is the best situation, high input voltage/low duty cycle, or low input voltage/high duty cycle? Let’s take an example of a design created in Texas Instruments’ WEBENCH Power Designer using different input voltages to modulate the duty cycle while looking at FET power dissipation losses. In Fig. 9, a graph of the high side FET behavior shows the AC losses decreasing significantly when going from 25% to 40% duty cycle whereas the DC losses increase only linearly. So somewhere around 35% duty cycle appears to be the ideal in order to be able to choose a FET with a balance of capacitance and RDS(ON). Continuing to lower the input voltage and go to higher duty cycles would give the lowest AC losses and highest DC losses, so at that point a FET with low RDS(ON) could be used with a tradeoff of higher gate charge. As shown in the graph in Fig. 10 for the low side FET, the DC losses are decreasing linearly when going from low to high controller duty cycle (resulting in shorter on time for the low side FET) and the losses are minimized at high controller duty cycle. AC losses are low across the board, so a FET with low RDS(ON) should be chosen for all cases.

HIGHER EFFICIENCY

Fig. 11 shows what happens to the overall efficiency when we combine the high side and low side losses together. We see that the lowest combined FET losses and best efficiency for this case are for the high duty cycle case. Efficiency went from 94.5% up to 96.5%. Unfortunately, to get the low input voltage, we had to lower the voltage of the intermediate voltage rail supply, which increased its duty cycle since it is being fed from a fixed input supply. So that may offset some or all of the gains made at the POL. Another option may be to not use an intermediate rail at all and go directly from the input supply to the POL regulator in order to reduce the regulator count. In that case the duty cycle will be low and the FETs must be selected carefully.

COMPARE RAIL VOLTAGES

The situation becomes more complicated in a power supply system with multiple output voltage and current requirements. To visualize the tradeoffs in such a system, we can use the WEBENCH Power Architect tool. This allows users to view a number of scenarios with different intermediate rail voltages to compare the efficiency, cost and footprint for different POL regulator duty cycles. Fig. 12 shows a system with an input voltage of 28V and 8 loads of 4 different voltages ranging from 3.3V to 1.25V. The three options to be compared include one with no intermediate rail with 28V direct from the input source to achieve low duty cycle at the POL regulators, one with 12V intermediate rail for medium duty cycle at the POL regulators, and one with 5V intermediate rail for high duty cycle at the POL regulators. Fig. 13 and Table 1 show the results.

In this case, the architecture with no intermediate rail supply had the lowest cost, the architecture with the 12V intermediate rail voltage had the best efficiency and the option with the 5V intermediate rail voltage had the lowest footprint. Thus, we see that for a large system such as this there was no clear trend for the design parameters as we saw in the single POL supply case. This is due to the potentially conflicting demands of multiple regulators, each with different current and voltage requirements at the load along with the intermediate rail regulator itself. The best way to examine the various tradeoffs is to use a tool such as the WEBENCH Power Architect.

A link to the WEBENCH tool can be found here.

References

WEBENCH Power Architect can be accessed using the multiple output voltages option from the WEBENCH panel on http://www.ti.com

Related Articles

Demystifying Power MOSFET's Avalanche Ruggedness

Selecting n-channel MOSFETs for High-Side Hot-Swap Control

About the Author

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: