Instruments target serial I/O links and DDR interfaces

High-speed-digital serial I/O links and DDR memory interfaces are presenting significant measurement challenges as fourth-generation standards emerge. As signals travel at ever higher speeds over digital interfaces, designers face signal-integrity challenges and need to be able to measure jitter and evaluate complex modulation schemes. Instruments including oscilloscopes, bit-error-ratio testers (BERTs), network analyzers, and protocol analyzers as well as hardware and software options all may have a role to play.

High-speed serial test challenges continue to grow as technology evolves. Addressing receiver test and calibration, Ellen Spindler, product marketing manager at Keysight Technologies, said, “Each interface defines a certain worst-case condition where the receiver must be able to detect the transmitted bits properly.” The test point at which the receiver test condition is defined with respect to parameters like input level, jitter, and interference has moved into the receiver IC, she said, so it cannot be directly accessed with oscilloscope probes any longer. “We have seen this for PCIe 3,” she said, “and expect this also for MIPI M-PHY gear 3, USB 3.1, and PCIe 4.” In addition, she said, “New digital data formats are popping up, other than the traditional non-return-to-zero (NRZ), to optimize bandwidth and reduce power consumption. Popular examples are PAM-4 on the network interfaces and a new three-wire MIPI C-PHY interface.”

Chris Loberg, senior technical marketing manager at Tektronix, commented on memory test. “One of the most significant developments for 2014 was the release of the LPDDR4 standard,” he said. “Compared to LPDDR3, the new specification presents a number of test and measurement challenges due to a lower input/output voltage of just 1.1 V, higher data rates, and compact mechanical designs that limit access to test points.”

Another concern is interoperability. “We are finding that more users are integrators buying parts from various vendors for their own boards,” said Roy Chestnut, product manager at Teledyne LeCroy. “They need quick verification that the system works as expected and do not necessarily need a full compliance package. Often, they are verifying functionality by using analysis tools such as eye diagrams. Interoperability needs validation, so protocol analysis is a unique method for interoperability testing.”

Cost also is an issue—both cost of test and cost of the serial interface implementation. “The cost of testing high-speed serial links with the instruments currently available on the market is too high,” said Chris Nunn, product manager for high-speed serial test at National Instruments. Added Mike Resso, product manager at Keysight, “Serial-bus testing has become very complex due to 28-Gb/s data rates, smaller design margins, and lower cost requirements.”

To address such challenges, Keysight offers the N1930B physical (PHY)-layer test system (PLTS 2014). With that product, Resso said, “We have addressed these issues with a full suite of features that help designers create faster channels in a shorter time to market and for less money.”

PLTS 2014, which shipped in February, can perform PHY-layer testing and characterization of high-speed interconnect and measure impedance, insertion loss, return loss, crosstalk, and skew. It can generate eye diagrams and supports conversion, RLCG modeling, and multichannel simulation.

BERT

BERTs also have a key role to play in high-speed digital test, and Anritsu has recently introduced the MU181500B jitter modulation source for its MP1800A 32-Gb/s multichannel BERT (Figure 1). According to Hiroshi Goto, business development manager at Anritsu, “The source generates wide-amplitude SJ up to 1 UI at a jitter frequency of 250 MHz, ensuring sufficient margin for receiver jitter tolerance tests. Additionally, the intrinsic jitter of typically 275-fs rms is extremely low for accurate measurements even at low jitter amplitudes.” He added that the MZ1834A/MZ1838A 4/8 PAM converter is another recently introduced option for the MP1800A. “The high-quality NRZ waveform of the MP1800A and wideband passive PAM converter generate high-quality PAM signals with assured S/N that make the solution well suited for high-speed backplane/interconnect applications,” he said.

Courtesy of Anritsu

Keysight also offers BERTs, including the J-BERT M8020A high-performance BERT for receiver characterization of single- and multilane devices running up to 16 or 32 Gb/s (Figure 2). Spindler said, “The complexity of RX test setups continues to increase with higher data rates—for example, de-emphasis is required in most interfaces operating above 5 Gb/s.” Other issues include closed eyes after the channel and the need to lock to lower rate system reference clocks using spread-spectrum clocking. To meet the challenges, the J-BERT M8020A, she said, “offers the highest level of integration,” with its built-in de-emphasis capability, four BERT channels, continuous time linear equalizer (CTLE), clock recovery capability, and a multiplying PLL for locking to reference clocks.

Courtesy of Keysight Technologies

Keysight’s new M8195A 65-GS/s arbitrary waveform generator is integrated into the M8000 Series BERTs, Spindler said, to support receiver testing and non-NRZ data formats. Beate Hoehne, new product introduction manager for the Digital & Photonic Test Division of Keysight, said the J-BERT M8020A and M8195A support 32 Gbaud and beyond.

“To maximize transmission within the PHY layer, you need to combine and optimize all dimensions for efficiency, cost, power, reach, reliability, and so on,” she said. “It is not clear what will be the right combination of symbol rate, bits per symbol, and number of carriers,” she continued, asking, “Will 32-Gbaud PAM4 or 32-Gb/s NRZ be the right solution? Will MIPI C-PHY or next-gen D-PHY be the right approach for mobile devices?” She concluded, “The M8195A provides the flexibility to support all the existing and new standards.”

Teledyne LeCroy’s Protocol Solutions Group focuses on high-speed serial communications test with several products, according to Chestnut. The SierraNet M408 with 40-GE native capture addresses the new 40-Gb/s Ethernet specification, he said. The SierraNet M408 handles Fibre Channel up to 16 G and 10-G/40-G Ethernet fabrics.

He added, “The Eclipse X34 M-PHY protocol analyzer and x4 SMA M-PHY interposer, along with M-PCIe protocol analysis software for M-PCIe protocol testing, support the MIPI M-PHY market addressing test needs for mobile platforms.”

In addition, he said, the Voyager M310 protocol analyzer and exerciser covers the new USB 3.1 specification with speeds to 10 Gb/s; it offers optional support for link-layer compliance tests. And finally, he said, for PCI Express Gen 3, the company has released new compliance tools with the Teledyne LeCroy PCIe 3.0 PTC.

Courtesy of Teledyne LeCroy

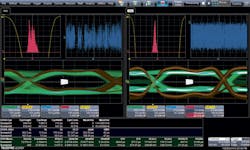

For memory applications, Teledyne LeCroy offers its DDR debug toolkit for use with certain Teledyne LeCroy oscilloscopes (Figure 3). The PHY-layer analysis package for DDR (DDR2/3/4 and LPDDR2/3) separates reads from writes. “This is the first step in analyzing DDR signals and a time-consuming process with the aid of analysis software,” said Robert Mart, product manager. “DDR debug toolkit effortlessly does so with a single button press.”

The DDR debug toolkit also deals with the simultaneous analysis of four measurement scenarios, presents up to 10 eye diagrams simultaneously while offering eye-mask testing and eye-parameter measurements, and supports DDR jitter analysis.

LPDDR test

Loberg at Tektronix listed several test offerings released over the past year, including a comprehensive test solution for LPDDR. He added, “Tektronix offers integrated PHY-layer testing and debug of the LPDDR4 standard in its DDR-LP4 analysis software. By automating test setup and execution, DDR-LP4 gives memory designers the confidence that they are in full conformance with memory standards.”

In addition, Tektronix released a test solution for HDMI 2.0 compliance test. “The successor to the widely adopted HDMI 1.4a/b standard, HDMI 2.0 is designed to meet the bandwidth requirements of forthcoming Ultra HD or 4K televisions while using existing cabling for backward compatibility,” Loberg said. “It significantly increases bandwidth to 18 Gb/s and adds such features as 32 audio channels and simultaneous delivery of video and audio streams to multiple users. As with previous HDMI versions, compliance and debug test solutions are critical to ensuring successful implementation of the specification.”

Compared with alternatives, Loberg said, “The Tektronix HDMI 2.0 test solution reduces test setup complexity through the use of a new automation framework for transmitter testing and a direct synthesis approach for receiver testing that eliminates the need for additional equipment like cable emulators and noise stressors. With the Tektronix AWG70000 arbitrary waveform generators, engineers can produce required receiver test signals and specified impairments automatically using direct synthesis methods which reduce test setup time and additional instrument cost.” He added that Presto Engineering has adopted Tektronix’s HDMI test solution. (See the Executive Insight in the January 2015 issue for more on how HDMI test fits within Presto’s test and engineering services offerings.)

In addition, Loberg said, over the last year, Tektronix introduced a 40GBASE-CR4 debug and automated compliance solution and enhanced IBIS-AMI S-parameters modeling support for Tektronix oscilloscopes. The company also debuted 40-Gb/s high-performance BERT for datacom and long-haul testing, a new BERTScope model to address 100G optical receiver test, and MIPI mobile protocol decode solutions for oscilloscopes.

Also addressing MIPI is Rohde & Schwarz. The company recently introduced the R&S RTO-K40 option for the R&S RTO high-performance oscilloscopes; the option addresses the need for fast analysis and testing of MIPI RFFE (RF front-end) interfaces. It also offers automatic glitch rejection. The R&S RTO-K40 option allows users to directly trigger on content such as “extended register write” or error states such as “bus park error” of the MIPI RFFE protocol. The decoded protocol content is displayed in an easy-to-read color-coded overview as well as in tabular format. A search and navigation function helps users to track even long records and directly jump to positions of interest in the protocol.

Courtesy of National Instruments

National Instruments recently introduced the PXIe-6591R and PXIe-6592R high-speed serial instruments (Figure 4), which include an open, user-programmable FPGA to offer sufficient flexibility for testing both standard and custom serial interfaces.

Addressing cost of test, Nunn at NI said, “Oscilloscopes and bit error rate testers often are too expensive and slow to justify the coverage they provide while protocol-specific hardware often is not flexible enough to integrate into automated test systems. With the introduction of the PXIe-6591R and PXIe-6592R, we bring protocol-aware test solutions to the market at one-tenth the cost of traditional high-speed serial test solutions along with the added benefits of the PXI platform. One of the PXI benefits includes tight synchronization with other PXI modular instruments such as oscilloscopes, which results in a highly integrated and complete test solution.”

DesignCon 2015, scheduled for Jan. 28-29 in Santa Clara, CA, will offer an opportunity to explore high-speed digital test further. Keysight will be showing the J-BERT M8020A with new generator performance and capabilities, Spindler said. Hoehne added that the company also will show the AWG M8195A used for PAM4 signal generation and analysis. And Resso said the PLTS 2015 release will be demonstrated; it will include new features such as Save State and Round Robin as well as support for PXI.

Goto said, “Anritsu will be displaying three solutions for high-speed interconnect testing at DesignCon 2015. The signal-integrity test solution will feature the MP1800A BERT along with the VectorStar vector network analyzer (VNA) and MP1825B 4-tap Emphasis. We also will be displaying a 100G AOC test solution featuring the MP1800A. Our third station will include a 65G PAM4 BERT.”

According to Nunn at NI, “We plan to show the PXI-6591R controlling a TI DAC38J84 high-speed DAC through the JESD204B protocol. The Xilinx GTX transceivers on the PXIe-6591R and PXIe-6592R high-speed serial instruments support a broad variety of protocols, and NI provides a number of software examples to demonstrate how to integrate common protocols as well as LabVIEW architectures for several application patterns.”

Chestnut said Teledyne LeCroy will exhibit its DDR, USB3, and PCIe test solutions as well as the HDO high-definition oscilloscopes and the recently launched 100-GHz 10Zi oscilloscope. “We also will present our Voyager M310 analyzer/exerciser, the PCIe Summit T3-8 and Summit Z3-16 exercisers, and the Kibra 480 compliance and protocol analyzers,” he said.

According to Loberg, “The Tektronix DesignCon 2015 presence includes a combination of technical paper presentations, panel moderation, and a large show-floor exhibit with educational demonstrations.” Common themes that will resonate in these activities, he said, include embedding and de-embedding techniques needed to preserve signal margins and approaches to testing in accordance with new 100 G standards (28 Gb/s, 56 Gb/s) coming into the serial communications industry.”

For More Information

About the Author

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: