Teledyne LeCroy touts high-speed test at DesignCon

Santa Clara, CA. Teledyne LeCroy chose DesignCon to introduce several new products, including the HDA125 high-speed digital analyzer for its oscilloscope line, an interposer probe for analysis of PCIe External Cable 3.0 ports that utilize the new PCI Express External Cabling Specification Revision 3.0, and the Power Delivery Compliance Suite for the Voyager M310C SuperSpeed USB 3.1 protocol verification platform.

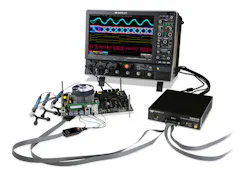

The HDA125 digital acquisition system captures 18 channels of digital data at 12.5 GS/s. Adding it to Teledyne LeCroy oscilloscopes by means of the LBUS interface architecture results in a flexible, high-performance mixed-signal solution. Also announced was the QuickLink probing system, featuring low-cost, high-fidelity probe tips that work with both the HDA125 and Teledyne LeCroy WaveLink probes using the new Dxx30-QL QuickLink adapter.The HDA125 samples 18 input signals at 80 ps intervals (12.5 GS/s) for accurate characterization of the fastest signals. However, sample rate is only half the story—high-speed embedded systems testing often poses challenging signal amplitude conditions. The High-speed Digital Analyzer meets these challenges with a 3-GHz digital leadset, ultra-low probe loading, and 150-mV minimum signal-swing sensitivity. The system ensures precise digital signal interpretation with a unique hysteresis adjustment capability.

The QuickLink probe tip system is designed from the ground up to be compatible with both the HDA125 High-speed Digital Analyzer and with Teledyne LeCroy’s WaveLink series of differential analog probes. This cross-connection capability allows a device under test (DUT) to be equipped with QuickLink Solder-In (QL-SI) tips at all desired test points, enabling swapping of connections between digital and analog acquisition systems as needed.

Unlike other consumable probe tip solutions that rely on tiny, delicate tips located very close to the DUT, the QL-SI tip has an integral 9-inch lead. When connected to a WaveLink analog probe using the new Dxx30-QL adapter, QuickLink tips provide 6 GHz of bandwidth and a flat, well-controlled frequency response. Used for digital acquisitions with the HDA125, they support 3 GHz bandwidth with industry-leading sensitivity. In both cases, high input impedance (110-kΩ, 0.12-pF differential) ensures minimal loading of the DUT.

Teledyne LeCroy already offers a dedicated DDR Debug Toolkit, designed to simplify challenging memory interface validation. Adding the HDA125 allows the DDR command bus to be directly acquired and integrated into the analysis, enabling advanced command triggering and sophisticated, searchable bus state viewing. This is complemented by the intrinsic flexibility and performance of the QuickLink probing system, which allows easy transitions between digital and analog acquisitions of the signals under test.

The HDA125 is available in two models. The HDA125-18-LBUS is supplied with a full 18-channel leadset (including 18 QL-SI probe tips), and is priced at $20,900. For applications requiring fewer channels, the HDA125-09-LBUS is supplied with a 9-channel leadset (including 9 QL-SI probe tips), and is priced at $17,900. The HDA125 will initially be compatible with WaveMaster, SDA, and DDA 8Zi series oscilloscopes; compatibility with other instruments will follow.

The Dxx30-QL connects QL-SI probe tips to Dxx30 8-13 GHz WaveLink differential probe series and is priced at $850. A QuickLink “starter pack,” the Dxx30-QL-3SI, is priced at $1390 and consists of one Dxx30-QL adapter and three QL-SI tips. Support for the QL-SI tip on 4-6 GHz WaveLink differential probes will be added in the spring of 2016.

Delivery time on the above products is approximately 8-10 weeks ARO. Find more information on Teledyne LeCroy’s DDR test solutions at http://teledynelecroy.com/ddr/.

Interposer probe for analysis of PCIe

Teledyne LeCroy also announced the availability of an interposer probe for analysis of PCIe External Cable 3.0 ports that utilize the new PCI Express External Cabling Specification Revision 3.0, developed by the PCI-SIG. The PCIe External Cable 3.0 Interposer, which is used with Summit Protocol Analyzers, enables PCIe bus traffic between a system board and storage devices using PCIe External Cable 3.0 cables to be monitored, captured, and recorded for protocol analysis. The PCIe External Cable 3.0 interposer will support analysis for PCIe host interfaces such as SATA Express (AHCI/PCIe) and NVM Express (NVMe) at data rates from 2.5 GT/s up to 8 GT/s, and link widths from x1 to x8. For x16 link widths two PCIe External Cable 3.0 interposers can be used together with two synced protocol analyzers to show all transaction data.

The new PCIe External Cable 3.0 class cables are becoming the new standard for external cables for storage and enterprise systems. This cable type is defined in the PCI Express External Cabling Specification Revision 3.0, developed by the PCI-SIG. One cable can manage link widths from x1 to x4. Larger link widths can be achieved by adding additional cables. For example, a x8 link combines two x4 links. The technology supports PCIe 3.0 speeds, enabling high I/O throughput while providing the necessary cable management demanded by next generation systems.

This cable also uses the Cable Management Interface (CMI), which is important to storage systems because it allows in-band host software to communicate with an NVM subsystem through sideband signaling to provide out-of-band control and monitoring of device specifics. The PCI Express External Cabling Specification 3.0 uses an I2C interface to enable discovery of the cabling characteristics, to allow passage of sideband signals such as PERST# and WAKE#, and to enable future functionality such as NVME-MI, the Non-Volatile Memory Management Interface.

The PCIe External Cable 3.0 Cable Interposer supports I2C sideband signaling by passing it electrically through the link. The sideband signaling PERST# and WAKE# and other functionality can be monitored by the protocol analyzer through the interposer, where protocol issues and performance metrics can be analyzed and debugged. RefCLK# signals external to the cable are available on the PCIe External Cable 3.0 interposer for use with the protocol analyzer.

In addition to the new interposer, an adapter is also available for testing devices that use the SFF-8644 connector with PCIe External Cable 3.0 class cables. The adapter is a PCIe half-width CEM form factor plug-in card that allows connection of a PCIe External Cable 3.0 device to a standard PCIe slot. The adapter supports x1 to x16 link widths (using up to four PCIe External Cable 3.0 class cables) at speeds up to 8 GT/s.

“Managed cable topologies like the new PCIe External Cable 3.0 class cables are part of the advanced infrastructure of NVMe Management,” said John Wiedemeier, product marketing manager in the Protocol Solutions Group, Teledyne LeCroy. “This new probing and adapter solution will support the new PCIe External Cable 3.0 specification for cabling technology of next generation high speed storage systems that incorporate NVMe SSD devices.“

In 2010, Teledyne LeCroy introduced a PCI Express protocol analyzer supporting NVM Express (NVMe), a new PCI Express storage decoding standard. Since that time Teledyne LeCroy has added decoding for both SCSI Express (SOP/PQI) and SATA Express (AHCI/PCIe), and also specific probing for SFF-8639 connector-based storage system and devices. Integrating all three PCIe SSD technologies into a single protocol analyzer and adding targeted storage probing solutions gives developers versatile tools that can show essential details regarding proper data transmission and bus performance. These tools have been critical for much of the PCIe SSD interoperability testing that has occurred over the last few years.

The PCIe External Cable 3.0 Interposer and PCIe External Cable 3.0 Adapter are each available to order now.

Power Delivery Compliance Suite

And finally, the company announced the release of the Power Delivery Compliance Suite for the Voyager M310C SuperSpeed USB 3.1 protocol verification platform. Based on the Power Delivery (PD) Compliance Plan v1.0, this automated test suite allows developers to verify functionality, error recovery, and compliance for PD chipsets and end-products.

Integrated in Teledyne LeCroy’s flagship Voyager M310C USB 3.1 test platform, the Power Delivery Compliance Suite utilizes emulation scripts to mimic PD link partner behaviors. The system initiates and responds to PD messages while analyzing the real response from the device-under-test. It communicates directly over Type-C cabling and generates pass/fail reports to provide a fully automated test suite for Power Delivery protocol.

Built on the same open architecture as Teledyne LeCroy’s USB 3.1 Link Layer test suite, the PD Compliance Suite includes full source code for all PD test cases. This provides developers with a comprehensive library of test scripts that can be easily re-purposed for custom test development. The Power Delivery Compliance Suite addresses chapter 5 physical layer, chapter 6 protocol layer, and chapter 7 power supply test cases from the USB Power Delivery 2.0 Specification. As the test specifications are updated for Power Delivery 3.0, any software updates will be provided at no cost to PD Compliance Suite end-users.

“The release of the new PD Compliance Suite is another proof point that Voyager M310C remains the gold standard in test and verification for the USB developer community,” said Joe Mendolia, vice president of marketing at Teledyne LeCroy’s Protocol Solutions Group. “Designed from the outset to address the range of USB 3.1, Type-C and Power Delivery test specifications, the Voyager M310C platform allows developers to pre-test their devices for USB compliance. The slogan ‘know-before-you-go’ means designers can uncover compliance issues before beginning the certification process and gain additional confidence that their products will interoperate with other USB devices.”

The first protocol analyzer solution to feature native USB Type-C connectors, the Voyager M310C combined with the Power Delivery Compliance Suite can test PD enabled electronic markers as well as full-featured PD chipset implementations. The exerciser can emulate a full 100-W source or 100-W sink (with added programmable load). It can precisely direct devices into PD role swap and alternate mode behaviors. The system provides real-time voltage and power monitoring to provide continuous VBUS measurements for verifying power transitions and timing.

USB Protocol Suite Version 7.26 is also now released for the Voyager M310C system. This release adds support for numerous Power Delivery enhancements including ability to inject and trigger on errors in PD message frames. To simplify Power Delivery debug, this release automatically reports PD errors in the Traffic Summary; and provides a new real-time PD Status View showing state transitions on the USB Type-C Communication Channel.

About the Author

Rick Nelson

Contributing Editor

Rick is currently Contributing Technical Editor. He was Executive Editor for EE in 2011-2018. Previously he served on several publications, including EDN and Vision Systems Design, and has received awards for signed editorials from the American Society of Business Publication Editors. He began as a design engineer at General Electric and Litton Industries and earned a BSEE degree from Penn State.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: