All digital phase-locked loop offers sub-mW power consumption

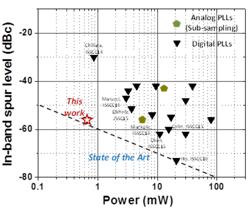

San Francisco, CA. At the 2017 International Solid-State Circuits Conference in San Francisco, imec, Holst Centre, and ROHM presented an all-digital phase-locked loop (ADPLL) for Internet-of-Things (IoT) radio transceivers. Whereas a PLL is traditionally one of the major power consumers in a radio and can take up to 30% of the radio area, this new ADPLL features a small area (0.18 mm² in 40-nm CMOS) and low power consumption (0.67 mW). All spurs are lower than -56 dBc and jitter is below 2 ps—beyond state-of-the-art digital PLLs.

The intuitive IoT relies on tiny sensor nodes, invisibly embedded in our environment and wirelessly connected to the internet. As billions of IoT devices are set to be deployed, battery replacement becomes impossible and therefore, power consumption reduction, especially in wireless connectivity, is one of the leading concerns and challenges on low power radio design to address.

The PLL is the radio component for frequency synthesis and has traditionally been an analog component, although the research community has been working on digital alternatives. All-digital PLLs enable a smaller footprint, better control and testability, and improved scaling to advanced CMOS nodes. However, to-date, they have lagged behind in terms of performance, compared to analog solutions.

Imec and ROHM’s all-digital PLL is an industry-first, combining record-low power consumption of only 0.67 mW, with state-of-the-art performance. It supports all specifications of Bluetooth low energy (BLE) radios while significantly reducing cost and power consumption below any of today’s solutions. This dividerless fractional-N digital PLL features a power-efficient spur-mitigation technique and a digital phase unwrap technique. Both approaches contribute to its performance.

“We are pleased of our collaboration with ROHM to solve yet another challenge and deliver an ADPLL that adds to imec’s world-class record low power radio design portfolio. With this performance, this all-digital PLL has become a mature and superior alternative to the widespread analog PLLs,” commented Kathleen Philips, program director at imec/Holst Centre for Perceptive Systems for an intuitive IoT. “The ADPLL is ready for industrial mass production and is currently being transferred to our industrial partners for product integration.”

At ISSCC2017, imec is presenting four papers addressing key building blocks for ultra-low power connectivity. The innovations serve power reduction in active, standby, sleep, and transient operation of standard radios like Bluetooth, or newcomers in the sub-GHz communication space.

“We are proud that we have developed the world-class low-power ADPLL with imec. We develop the RF transceiver with this ADPLL and integrate ROHM’s ultra-low power sensors and micro controllers into the “sensor edge” module. We hope they will be leaders of IoT market.” commented Isao Matsumoto, director, LSI Production Headquarters/LSI Product Development Headquarters at ROHM.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: