Thinking outside the box can lead to some interesting solutions. Sometimes the ideas turn out to be really good. Micron, Somnium, and Spansion have technology that fit this characterization.

Automata Rules

Micron Automata Processor (see “Automata Processor Piques Parallel Processing”) is now available featuring the SDK (software development kit) that includes the ANML “animal” (automata network markup language) compiler. ANML provides a more powerful mechanism than the more familiar regular expression that is also supported by the Automata Processor (AP).

This file type includes high resolution graphics and schematics when applicable.

The AP now has a 512-vector cache that allows the AP to handle 512 simultaneous input streams. It can process 128 million symbols/s. The chip contains almost 50K state transition elements (STE). It can match over 6000 sequences and there are six independent result regions. The chip has only a 4-W TDP.

The AP is ideal for packet processing, implementing pattern-based rules, and a host of other applications that are just being developed.

Linking Optimization

Program optimization can take place in a number of areas. The compiler can optimize source code. Code generators can perform micro optimization and there are global or whole program optimizers. Some just-in-time (JIT) compilers perform multiple optimization passes based on run-time profiling.

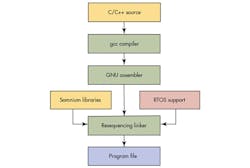

Somnium’s DRT (device-aware resequencing tools) uses the normal design flow (see the figure), but it employs an optimized gcc compiler and linker that perform global optimization. The compiler provides hints to the linker that in turn optimizes the code sequences that wind up in the executable. Hints about the target RTOS as well as Somnium DRT optimized libraries can be mixed with an application to create an optimized executable. The tools are supported with Eclipse IDE plug-ins. Freescale Kinetis and i.MX platforms are the initial target for these tools.

DRT can reduce code size up to 25% while providing better performance. DRT can handle processor interaction with platforms like the Cortex-M7 that can employ a Non Uniform Memory Architecture (NUMA).

Hosting HyperBus

Spansion’s new Traveo microcontroller targets automotive HMI (human-machine interface) applications. It is based on a Cortex-R5 core and it has plenty of connectivity support like CAN and automotive Ethernet. There is a 2D/3D graphics engine that can take advantage of lots of memory, but like many SoCs it uses off-chip memory for this aspect of the solution. HyperBus (see “How HyperBus Delivers 330 Mbyte/s Using a Dozen Signals”) is one of the interfaces on the Traveo that is available to developers.

HyperBus has an 8-bit data bus that uses about twice the number of signals of quad SPI (QSPI). It also has a bandwidth over 300 Mbytes/s compared to QSPI and other alternatives that run under 100 Mbytes/s. Spansion initially delivered flash-based HyperBus chips, but RAM versions are now available.

Traveo and HyperBus fill a niche between microcontrollers and higher-end microprocessor solutions. DDR3 and DDR4 can deliver faster memory platforms but with a higher monetary and power cost.

This file type includes high resolution graphics and schematics when applicable.

These three technologies do not take the normal approach, but they deliver better performance, cost, and efficiency compared to alternatives. Sometimes choosing the non-standard solution may be the best alternative.

About the Author

William G. Wong

Senior Content Director - Electronic Design and Microwaves & RF

I am Editor of Electronic Design focusing on embedded, software, and systems. As Senior Content Director, I also manage Microwaves & RF and I work with a great team of editors to provide engineers, programmers, developers and technical managers with interesting and useful articles and videos on a regular basis. Check out our free newsletters to see the latest content.

You can send press releases for new products for possible coverage on the website. I am also interested in receiving contributed articles for publishing on our website. Use our template and send to me along with a signed release form.

Check out my blog, AltEmbedded on Electronic Design, as well as his latest articles on this site that are listed below.

You can visit my social media via these links:

- AltEmbedded on Electronic Design

- Bill Wong on Facebook

- @AltEmbedded on Twitter

- Bill Wong on LinkedIn

I earned a Bachelor of Electrical Engineering at the Georgia Institute of Technology and a Masters in Computer Science from Rutgers University. I still do a bit of programming using everything from C and C++ to Rust and Ada/SPARK. I do a bit of PHP programming for Drupal websites. I have posted a few Drupal modules.

I still get a hand on software and electronic hardware. Some of this can be found on our Kit Close-Up video series. You can also see me on many of our TechXchange Talk videos. I am interested in a range of projects from robotics to artificial intelligence.

Voice Your Opinion!

To join the conversation, and become an exclusive member of Electronic Design, create an account today!

Leaders relevant to this article: